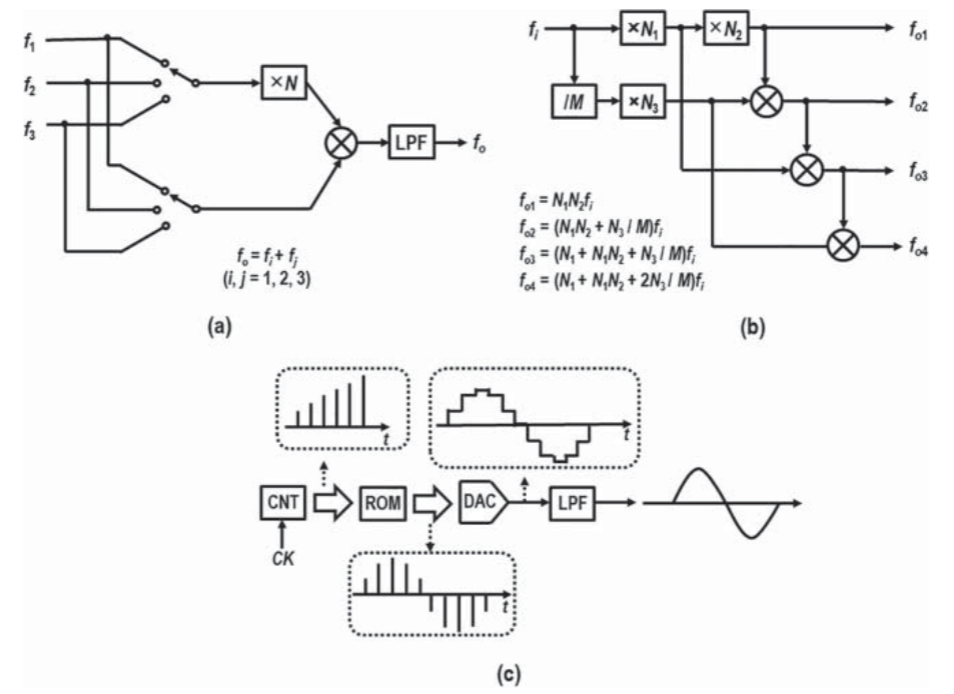

1. 直接频率合成

频率合成器是一种从单个或多个参考源产生一个或多个频率的设备。

- (a):第一代频率合成器,多个参考源,非相干

- (b):通过乘法器、分频器,相干产生多个频率。相干分为:直接法、间接法

- (c):现代方法:直接数字合成器(DDFS)

- DDFS具有良好的频率分辨率和快速的稳定时间

- 输出频率可以在单个时钟周期内合成。

- 与基于锁相环的频率合成器不同,DDFS的输出频率应低于输入频率的一半,以满足奈奎斯特采样准则。

- DDFS类似于可编程分频器,而基于锁相环的频率合成器类似于可编程倍频器。

- 无线收发器中使用的大多数频率合成器都是基于基于锁相环的频率合成,以低功率和小面积产生高频。

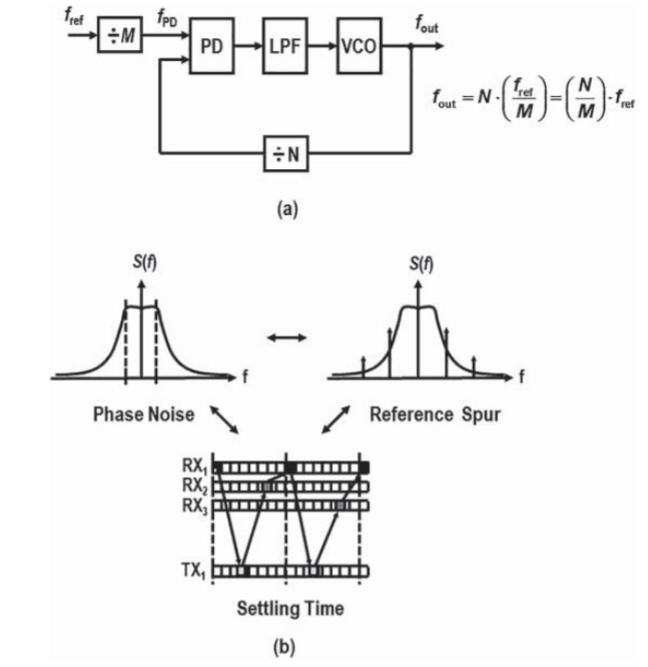

2. 间接频率合成:PLL

锁相技术保证锁相环输出频率的精度与参考源一样好,

通过在参考和反馈路径中设置数字计数器,使得间接相干频率合成。

由上图可以知:

不仅可以控制输出频率,还可以通过简单地改变M和N计数器的值来控制频率分辨率。

环路带宽由【相位噪声】【参考杂散】【建立时间】权衡得到。

- 对于参考杂散,由于它来自鉴相器或环路滤波器的漏电流,减小带宽是有帮助的。

- 窄带带宽使得锁相环难以抑制压控振荡器噪声。

- 此外,需要一个宽的带宽来快速锁定。

分频比对锁相环的整体性能有重要影响:

- 对于给定的输出频率,分频比越大,电荷泵、参考源的带内噪声越大。导致高积分相位误差

- 电荷泵对参考杂散的失配效应随着分频比的增大而增大

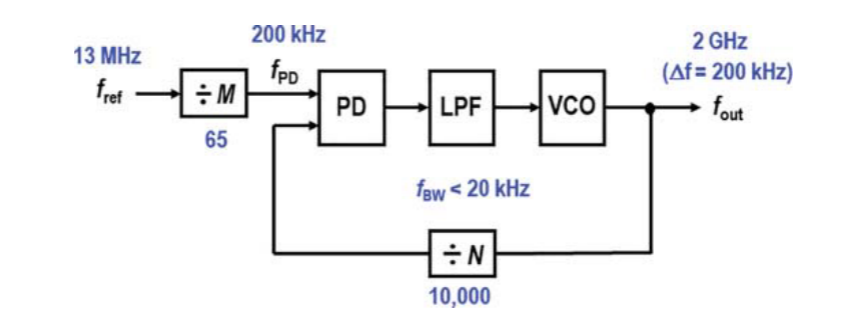

高分频比影响

- PLL产生2GHz的中心频率

- 频率分辨率为200 kHz

- 使用13 MHz的参考频率,则必须使用10,000的分频比,PD频率应与频率分辨率相同

- 要实现【-80dBc/Hz】带内相位噪声

- 噪声倍增系数:

- 则PD的相位噪声贡献应该小于【-160dBc/Hz= -80-80】

- 参考杂散

- 在输出电压的整个范围内,电荷泵失配应小于1%

- 为了稳定

- 最大环路带宽应当小于参考频率的15%

- 这使得难以实现带宽为30kHz(13MHz / 65 *15%)的敏捷频率合成

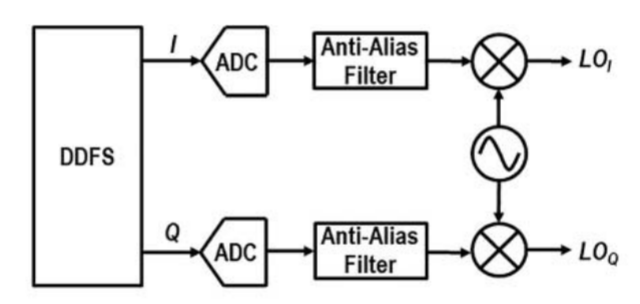

3. 高分辨率频率合成器结构

为了克服传统的基于PLL的频率合成器中信道间隔和PD频率之间的权衡,以下三种架构对于集成电路设计值得注意:

- 基于整数N PLL和DDFS的混合架构

- 多环路PLL架构

- 小数N分频PLL架构

基于整数N PLL和DDFS的混合架构

DDFS用于提供精细的频率分辨率和快速建立时间,而整数N PLL则产生用于上变频的载波频率。

整数N PLL不需要提供精细的频率分辨率,因此可以设计宽带PLL。

该架构由于片上混频器和DDFS的硬件复杂性而遭受高杂散生成。

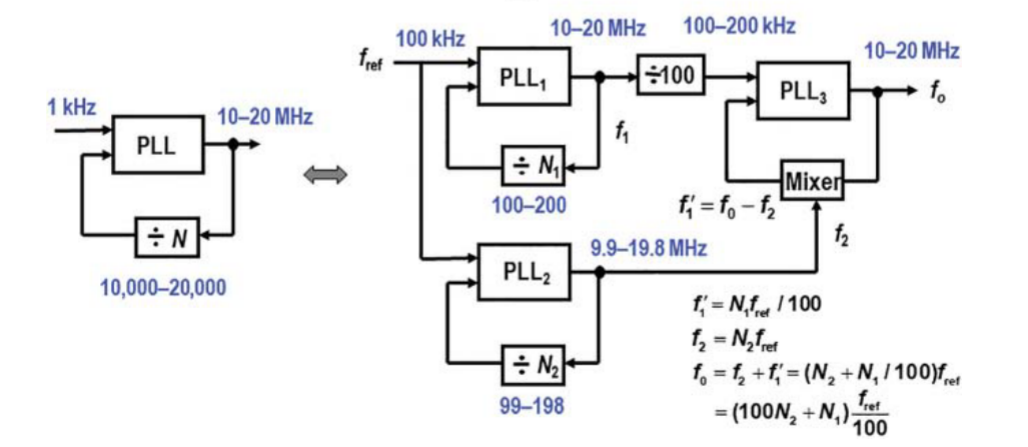

多环路PLL架构

- 如果单个PLL产生10~20MHz的频率范围

- 频率分辨率:1kHz

- 分频范围:10,000~20,000

采取多环路拓扑时:

- PLL1,产生10~20MHz频率范围,频率分辨率100kHz

- PLL2,产生9.9~19.8MHz频率范围,频率分辨率100kHz

- PLL1通过分频器,PLL2通过混频器与PLL3连接

与混合架构类似,硬件复杂性和混频器线性引起的杂散生成将是全集成多环PLL设计中的一个问题

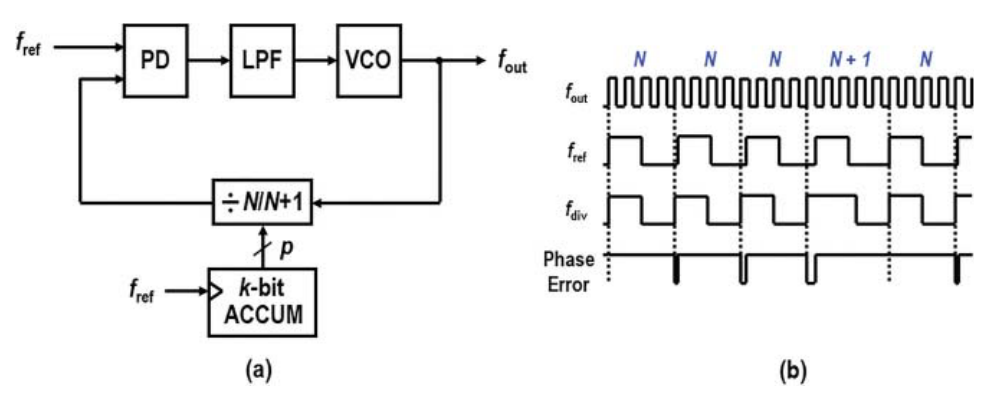

分数锁相环

小数N分频PLL通过调制分频比实现比PD频率更精细的频率分辨率。

- 双模分频器的周期性调制会在载波频率附近产生杂散。因此,提出了各种杂散抑制方法

- ΔΣ小数N频率合成器的开发为无线收发器系统带来了巨大的飞跃。通过基于伪随机数字调制产生输出频率,可以获得具有任意精细频率分辨率的无杂散频率产生。

4. 频率合成的系统设计方面

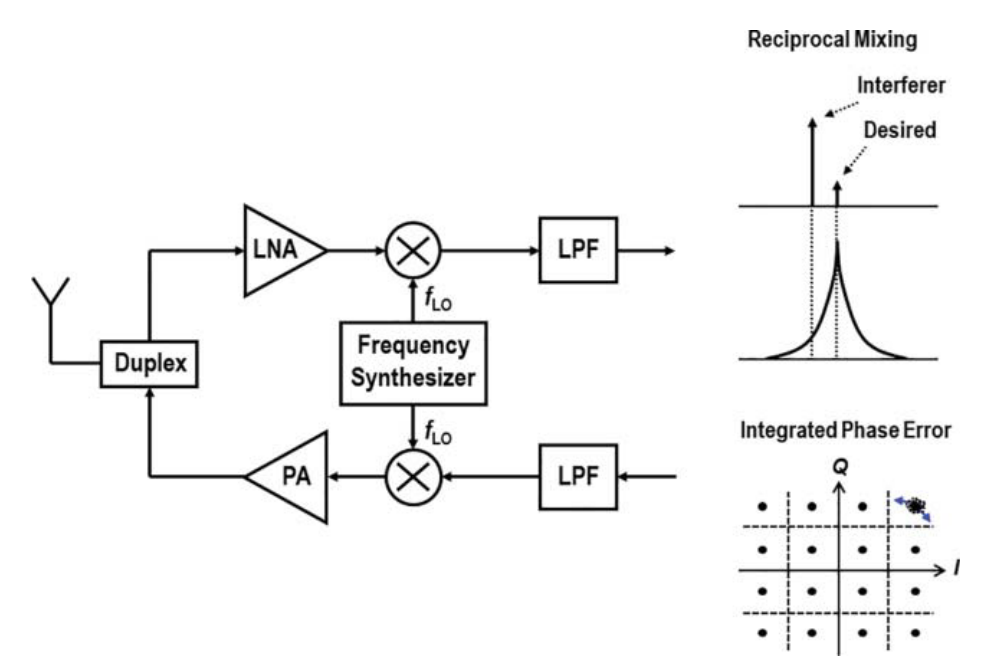

在无线收发器系统中,频率合成器是产生用于信道选择多个频率的关键构建块。

- 带内相位噪声对于实现低积分相位误差非常重要。

- 较大的积分相位误差会增加比特星座图中跨越判决边界的概率,从而降低BER性能

- 收发器还应考虑带外相位噪声

- 在发射机中,重要的是遵守由无线标准设置的频谱掩码

- 在接收机中,带外相位噪声可以与强干扰混合

- 由带外相位噪声下变频的干扰器可能破坏基带信号。这被称为【reciprocal

mixing effect】

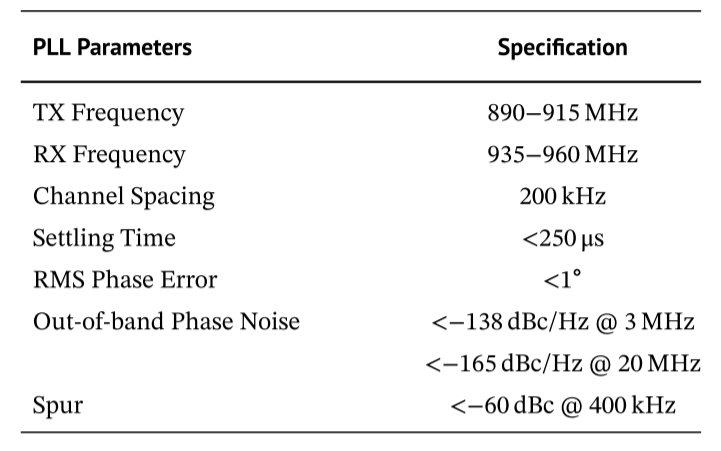

example GSM收发机的PLL设计考虑

GSM代表全球移动的通信系统

- chabbel spacing 200kHz。信道间隔200kHz,频率分辨率为200kHz,PD的频率为【200kHz】

- 960MHz的输出频率,最大分频比【4,800】

建立时间和带宽

快速变频,欠阻尼。

- 阻尼系数:

- 建立时间:

- 频率步进:

- 频率误差:

固有频率 fn:

时间常数 τ:

- 建立时间【250μs】几乎是固有频率相关的时间常数【10.7μs】的24倍。

- 主要是频率误差 100Hz,约为载波频率(960MHz)的0.1ppm(

)

假设是2阶2型PLL,【环路带宽】是:

这是得到如何通过手工计算获得临界系统参数的基本思路。必须使用PLL专用软件获得最终值。

带内相位噪声

对于给定的带宽,带内相位噪声由RMS相位误差的要求决定。

噪声带宽:

RMS相位抖动小于1°,带内相位噪声 Ni:

可以得到:

- 如果带内相位噪声优于−85 dBc/Hz,则可以增加环路带宽,以进一步改善建立时间。

- 增加环路带宽会降低杂散或带外相位噪声性能

杂散和带外相位噪声

在无线系统中,减轻来自其它信道的干扰是重要的。

- 在发射机中,定义频谱屏蔽以限制发射机输出的功率发射

- 在接收机中,应考虑相邻信道干扰、带内阻塞和带外阻塞信号,以最小化互易混频问题

对于GSM标准,所需杂散电平主要由发射机频谱屏蔽决定.

要求400 kHz偏移时的典型杂散电平为−65 dBc,附加系统裕度为5 dB,相当于200 kHz偏移频率时的参考杂散为−59 dBc。

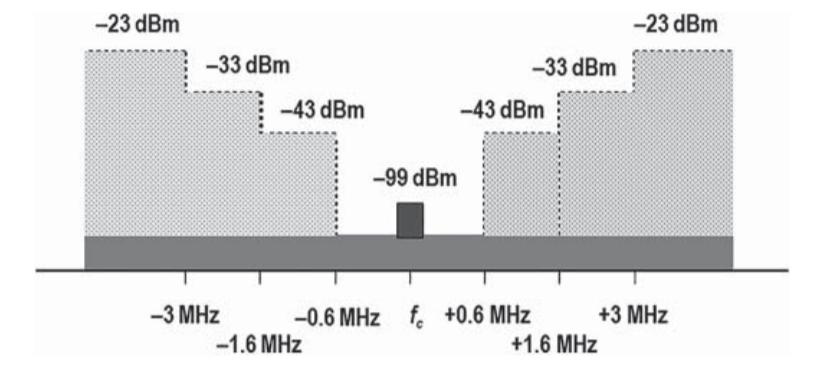

- 最困难的条件之一是在3 MHz偏移频率处满足阻塞信号的要求,其中阻塞信号高达−23 dBm,而期望信号功率仅为−99 dBm

- 高斯最小频移键控(GMSK)调制所需的信噪比(SNR)为9 dB,才能满足

的BER

- 在系统裕量为3 dB的情况下,频率合成器在3 MHz偏移下的噪声功率应比载波功率低88 dB

- 考虑到信号带宽为100 kHz

所需要的相位噪声:

由于发射机的很远的相位噪声可以扩展到接收机频带,所以非常远的带外相位噪声对于发射机也是关键的。

- 发射机中,在20 MHz偏移时需要− 160 dBc/Hz的相位噪声。

- 远偏移频率处的相位噪声完全由VCO噪声决定

- 设计低噪声VCO对于满足GSM系统的带外相位噪声要求至关重要。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?