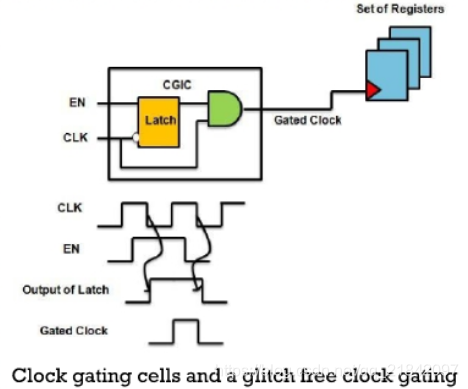

门控时钟是RTL级进行低功耗设计的最常用方法,能够有效降低动态功耗。在实际使用中,一般用ICG(集成门控时钟单元)来完成clock gating。ICG电路和时序如下:

通常来说,工艺库已经集成了ICG,在做门控时钟的时候其实不用考虑那么多。如果在实际设计中,工艺库未提供ICG,需要自己搭建一个门控时钟电路,那么在布局布线的时候可能要注意,不能将期间摆的太远,否则线延迟等会让这个结构失去其意义。

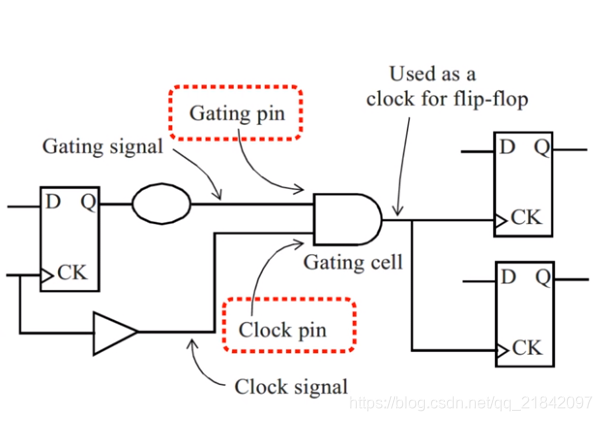

当门控信号控制了逻辑单元中时钟信号的路径时,我们会进行Clocl Gating check。我们根据下图了解一些定义,这样比较直观:

这里我们需要明确什么样的电路会被工具分析成为门控时钟:

- Gating cell的输出是作为时钟信号进行使用,即连接到了后级逻辑单元的时钟端口。

- Gating pin的输入非时钟信号;若Gating pin的输入为时钟信号,则其必须不连接后级逻辑单元的时钟端口。

- 对于上图简单的与门控制,工具可以较好的推断;但对于复杂结构,需要自己添加约束来进行检查。

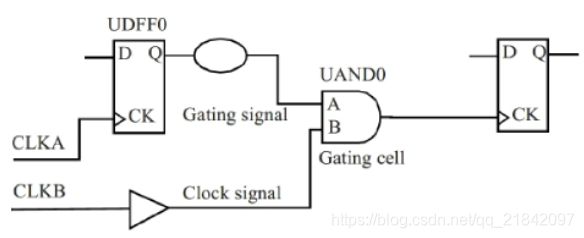

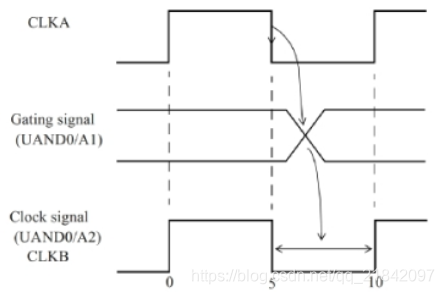

运用提到的定义,对于上图来说,CLKB才是clock signal。接下来我们以这个电路为例看看如何进行clock gating check(对于这个与门来说,有些类似于data to data check):

首先定义两个时钟

create_clock -name CLKA -period 10 -waveform {0 5} [get_ports CLKA]

create_clock -name CLKB -period 10 -waveform {0 5} [get_ports CLKB]

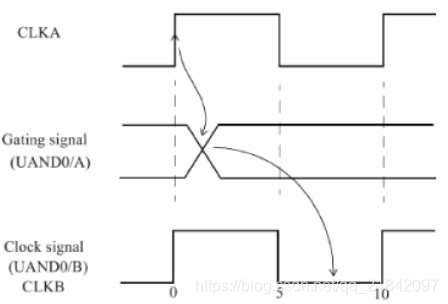

我们要保证时钟切换的时候不能产生一些毛刺,也不能产生对时钟有影响的结果。对于此电路来说,gating cell是一个与门,那么gating pin的信号变化只能发生在clock pin的低电平状态。则setup check要求门控信号在时钟信号变高前变化;hold check要求门控信号只能在时钟下降沿之后进行改变。时序图如图,

gating pin的变化要落在5-10ns间,才能满足门控时钟的要求。

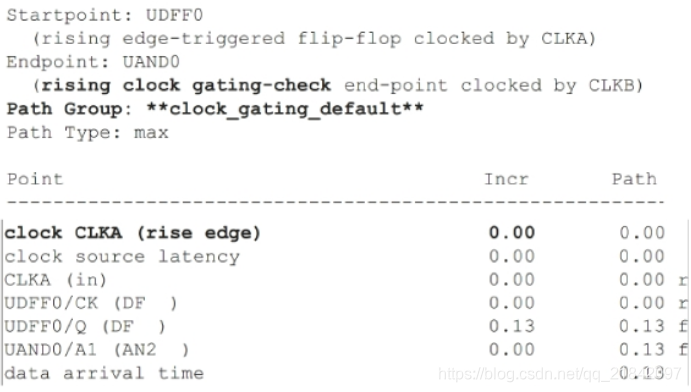

我们看看setup check的时序报告:

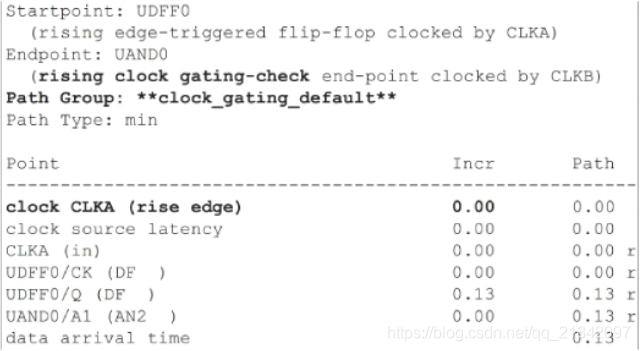

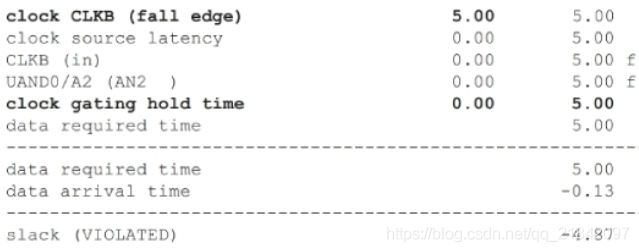

同样地,我们可以看看hold check的时序报告:

可以看到,在5ns时进行hold check是非常严苛的。由于gating signal的变化过于迅速,导致hold check失败。这个问题可以用我们前面提到的半周期进行处理。我们将寄存器的采样边沿改为负沿:

这样的话,gating signal在负沿launch,留给时序检查的周期就剩下了半个周期,较好满足hold time:

8126

8126

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?