You're familiar with flip-flops that are triggered on the positive edge of the clock, or negative edge of the clock. A dual-edge triggered flip-flop is triggered on both edges of the clock. However, FPGAs don't have dual-edge triggered flip-flops, and always @(posedge clk or negedge clk) is not accepted as a legal sensitivity list.

Build a circuit that functionally behaves like a dual-edge triggered flip-flop:

(Note: It's not necessarily perfectly equivalent: The output of flip-flops have no glitches, but a larger combinational circuit that emulates this behaviour might. But we'll ignore this detail here.)

我们现在对时钟上升沿与下降沿都已经很熟悉了。但是FPGA没有一个同时检测双边沿的触发器,而且always中的敏感列表也不支持(posedge clk or negedge clk)。

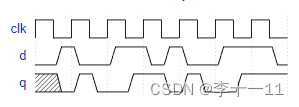

设计一个双边沿检测的触发器,时序如下图所示:

Module Declaration

module top_module (

input clk,

input d,

output q

);

本题有两中解题思路,一种是用MUX,一种是用XOR

MUX代码如下:

module top_module (

input clk,

input d,

output q

);

reg q1, q2;

//这里来实现clk的上升沿与下降沿

assign q = clk?q1:q2;

always @ (posedge clk)

begin

q1 <= d;

end

always @ (negedge clk)

begin

q2 <= d;

end

endmoduleXOR代码如下:

module top_module(

input clk,

input d,

output q);

reg p, n;

// clk的上升沿

always @(posedge clk)

p <= d ^ n;

// clk的下降沿

always @(negedge clk)

n <= d ^ p;

//在上升沿时候,p=d^n, 则q=d^n^n=d;

//在下降沿时候,n=d^p, 则q=p^d^p=d;

//加载一个新值时会取消旧值。

assign q = p ^ n;

// 这样写是无法综合的

/*always @(posedge clk, negedge clk) begin

q <= d;

end*/

endmodule

837

837

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?