外部存储器接口(EMIF)

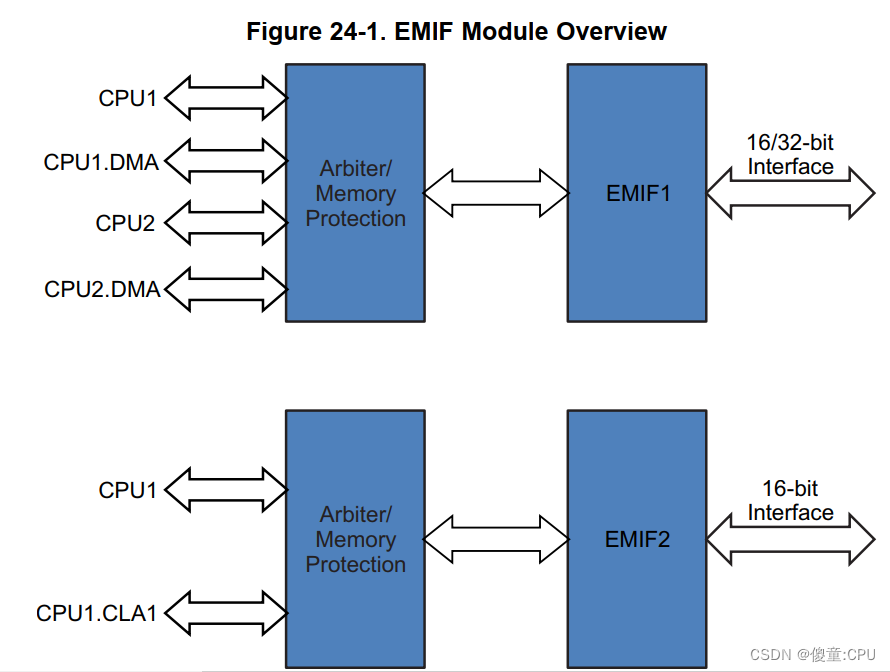

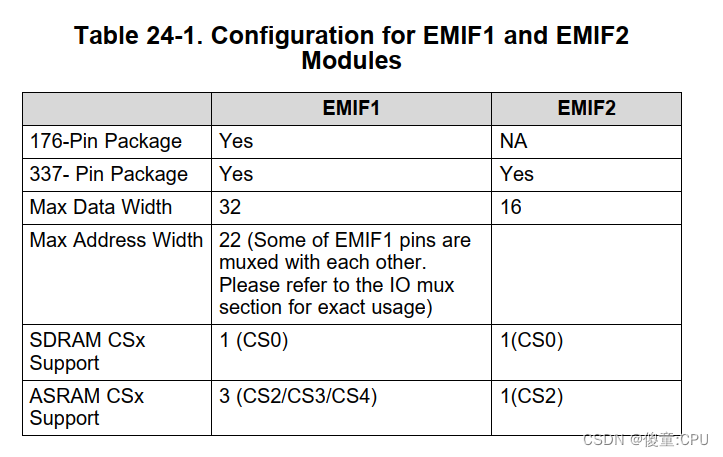

该设备支持双核架构;为了为每个CPU子系统提供一个专用的EMIF,该设备支持两个EMIF模块——EMIF1和EMIF2。两个模块完全相同,具有相同的功能集,但具有不同的地址/数据大小。EMIF1在CPU1和CPU2子系统之间共享,而EMIF2专用于CPU1子系统。

在该设备上,如果EMIF1被选择为具有32位数据宽度,则不能使用EMIF2,因为EMIF2数据引脚与EMIF1 MSB数据引脚复用。

外围设备的用途

该EMIF存储器控制器与JESD21-C SDR SDRAM存储器兼容,采用32位/16位数据总线。该EMIF的目的是为CPU提供一种连接到各种外部设备的方式,包括:

单数据速率SDRAM

异步设备,包括NOR闪存和SRAM

特性

EMIF控制器包括许多功能,以增强连接到外部SDR SDRAM和异步设备的方便性和灵活性。

支持异步内存

EMIF控制器支持异步:SRAM存储器;NOR闪存

有一个外部等待输入,允许较慢的异步存储器扩展存储器访问。EMIF模块支持多个芯片选择(启用)。每个芯片选择都具有以下可单独编程的属性:数据总线宽度;读取周期计时:设置、保持、选通;写入周期定时:设置、保持、选通;总线转换时间;可编程超时的延长等待选项;选择选通选项。

支持同步DRAM内存

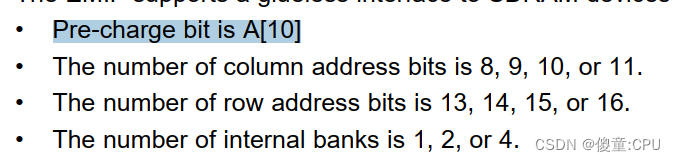

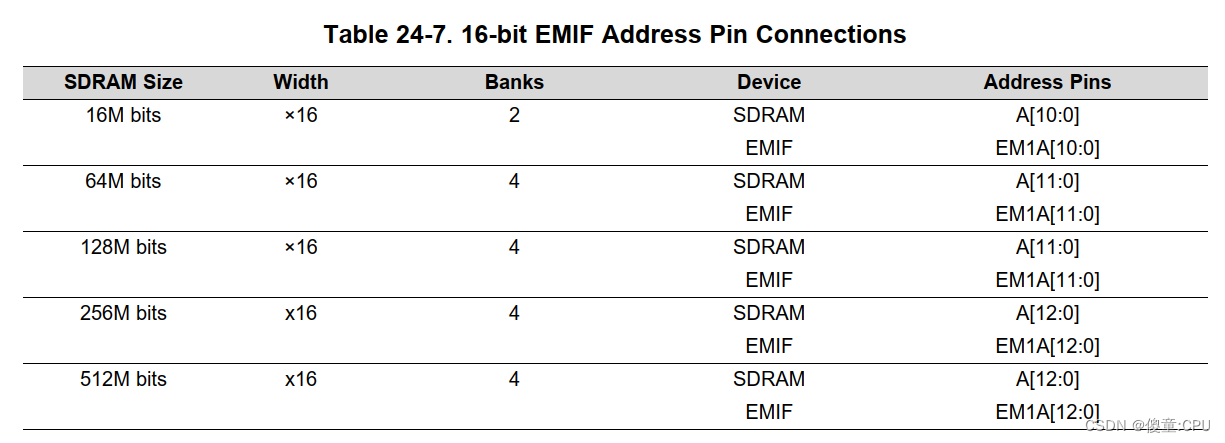

EMIF模块还支持16位/32位SDRAM。它有一个单一的SDRAM芯片选择。支持的SDRAM配置为:

•一、二和四组SDRAM设备

•具有八、九、十和十一列地址的设备

•两个或三个时钟周期的CAS延迟

•16位/32位数据总线宽度

•3.3V LVCMOS接口此外,EMIF支持将SDRAM置于自我刷新和断电模式。

自刷新模式允许SDRAM处于低功率状态,同时仍然保留存储器内容,因为即使没有来自微控制器的时钟,SDRAM也将继续刷新自己。断电模式可以实现更低的功率,但如果需要数据保留,微控制器必须定期唤醒并发出刷新。

请注意,EMIF模块不支持移动SDRAM设备

功能框图

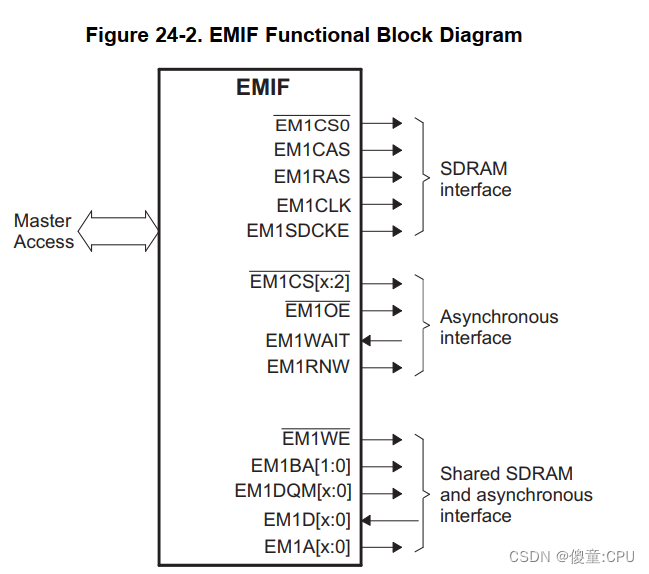

EMIF及其内部请求程序之间的连接,以及外部EMIF引脚。

包含MCU内部可以向EMIF发送请求的实体及其优先级的描述。

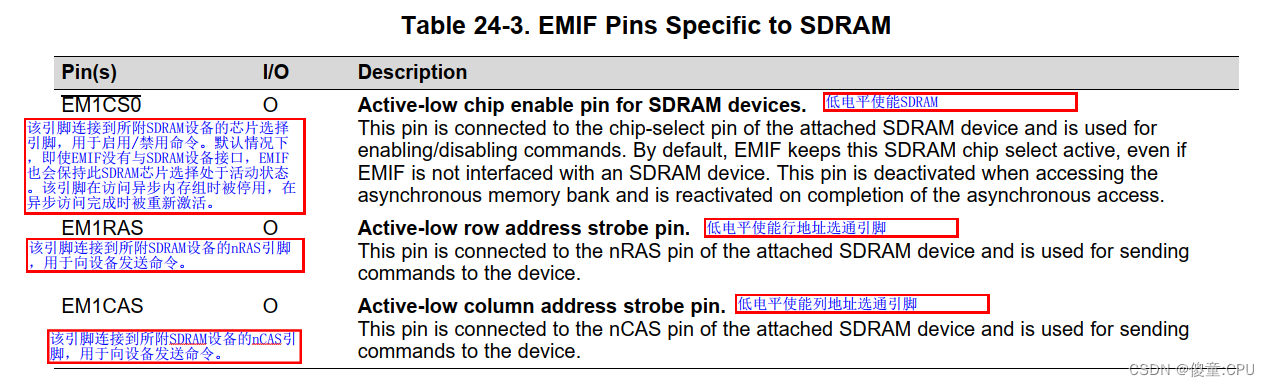

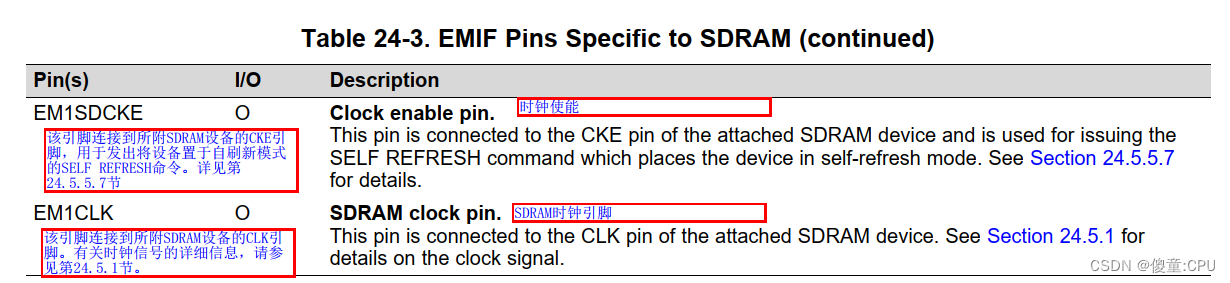

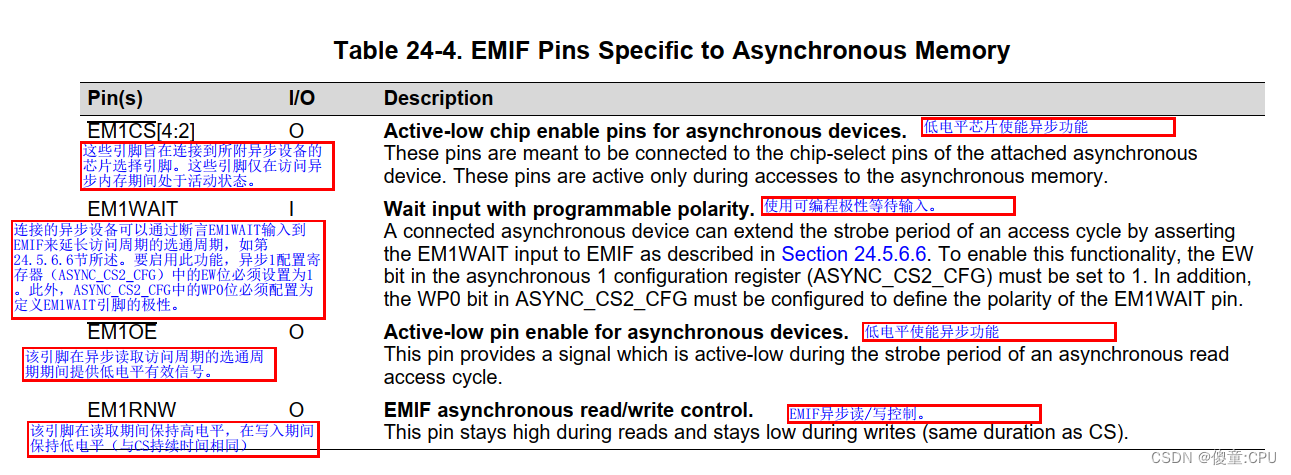

描述了EMIF外部引脚,并总结了它们与SDRAM和异步设备接口时的用途。

配置设备引脚

GPIO多路复用器寄存器必须配置为将此外围设备连接到设备引脚。为了避免引脚出现故障,必须首先配置GPyGMUX位(同时将相应的GPyMUX位保持为默认值零),然后将GPyMUX寄存器写入所需值。某些IO功能是由GPIO寄存器设置定义的,与此外围设备无关。对于输入信号,应通过将适当的GPxQSELn寄存器位设置为11b,将GPIO输入资格设置为异步模式。内部上拉可以在GPyPUD寄存器中进行配置。有关GPIO多路复用器和设置的更多详细信息,请参阅GPIO章节。

EMIF模块体系结构

提供有关EMIF的体系结构和操作的详细信息。SDRAM和异步接口以及其他与系统相关的配置(如时钟控制)都包含在内。

EMIF时钟控制

EMIF时钟在EM1CLK引脚上输出,应在与外部SDRAM设备接口时使用。EMIF模块获得PLLSYSCLK时钟域作为输入。用户可以通过配置时钟控制模块中PERCLKDIVSEL寄存器中的EMIF1CLKDIV字段,选择以PLLSYSCLK/1或PLLSYSCL K/2时钟频率运行EMIF。

EMIF请求

MCU内的不同来源可以向EMIF发出请求。这些请求包括对SDRAM存储器、异步存储器和EMIF寄存器的访问。EMIF一次只能处理一个请求。因此,高性能主仲裁块存在于MCU内,以向EMIF提供来自不同源的优先请求。来源如下:CPU1、CPU1.DMA。

如果同时从两个或多个源提交请求,交叉开关将首先向EMIF转发最高优先级的请求。在完成请求后,主仲裁块再次评估未决请求,并将最高优先级的未决请求转发给EMIF。

主仲裁块总是允许来自任何主的RD访问。但对于WR访问(或执行访问),主仲裁块仅允许来自CPU子系统的主控器访问,该CPU子系统基于存储器控制器模块中的EMIF1MSEL寄存器中的配置获取EMIF模块的主控所有权。

当EMIF收到请求时,可能会立即处理,也可能不会立即处理。在某些情况下,EMIF将在处理请求之前执行一个或多个自动刷新周期。有关EMIF在执行请求和执行自动刷新周期之间的内部仲裁的详细信息。

EMIF信号说明

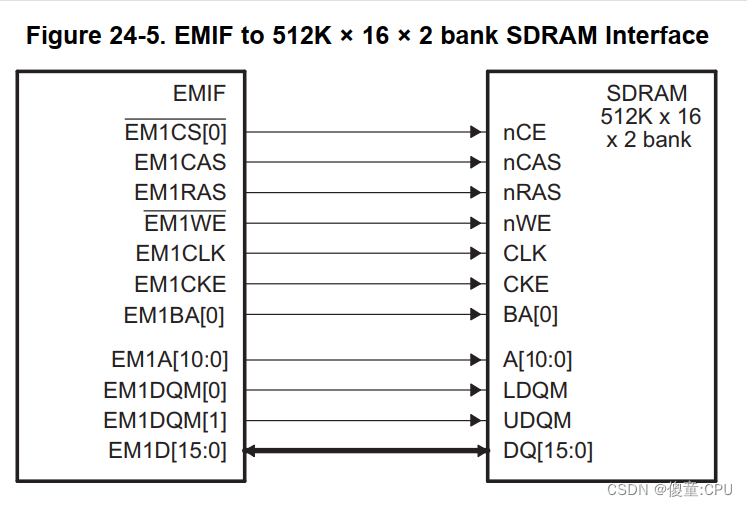

SDRAM控制器和接口

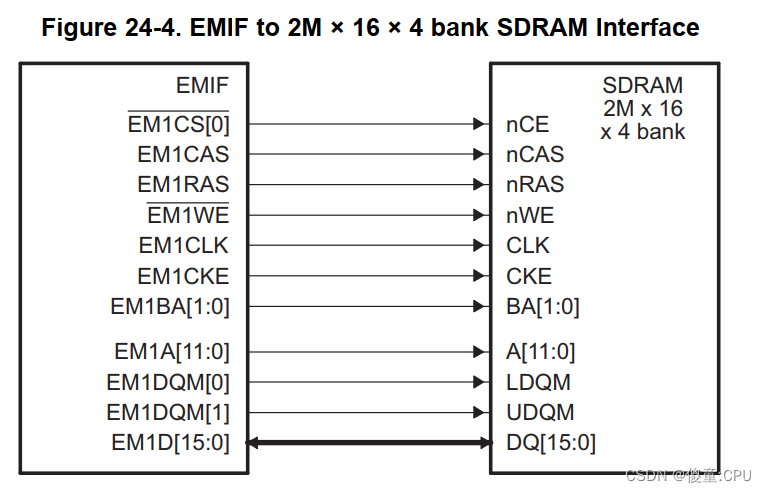

EMIF控制器为大多数标准SDR SDRAM设备提供无胶接口,并支持自刷新模式和优先刷新等功能。此外,它还通过可编程参数提供了灵活性,如刷新率、CAS延迟和许多SDRAM时序参数。以下部分详细介绍了如何接口和正确配置EMIF,以便对外部连接的SDR SDRAM设备执行读写操作。此外,提供了将EMIF与通用SDRAM设备接口的详细示例。

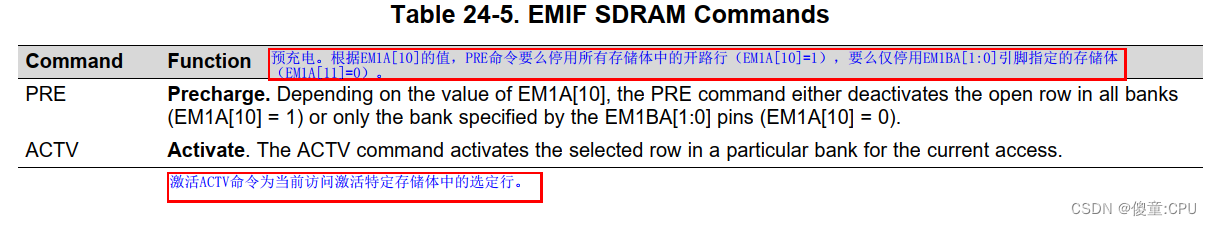

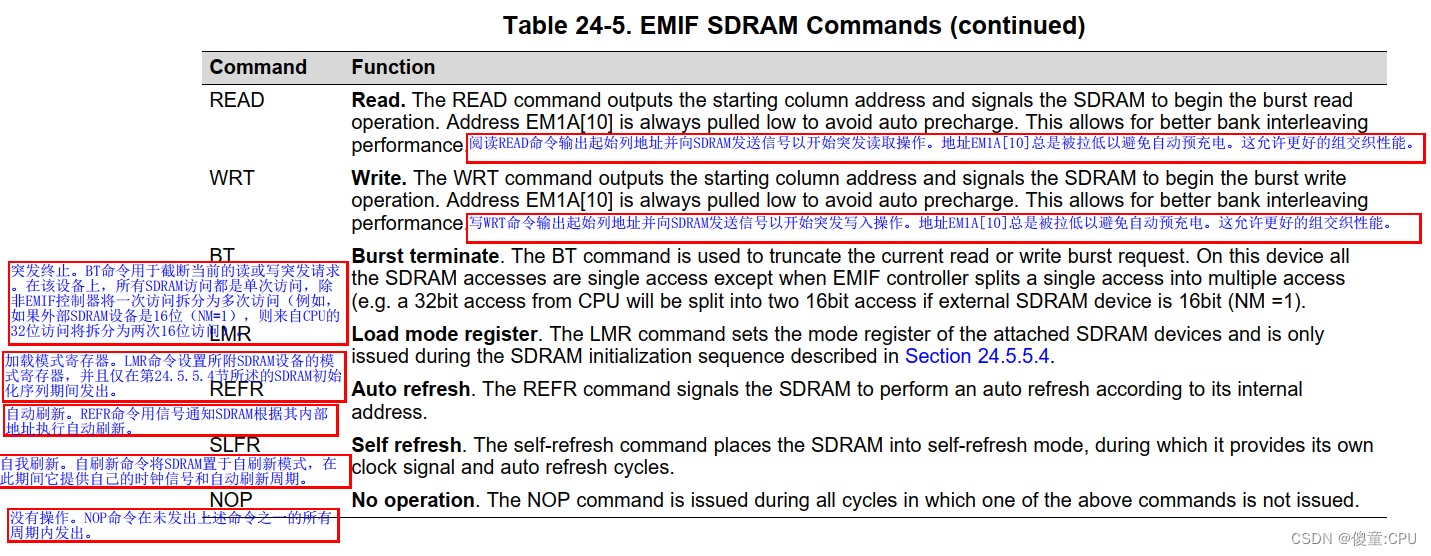

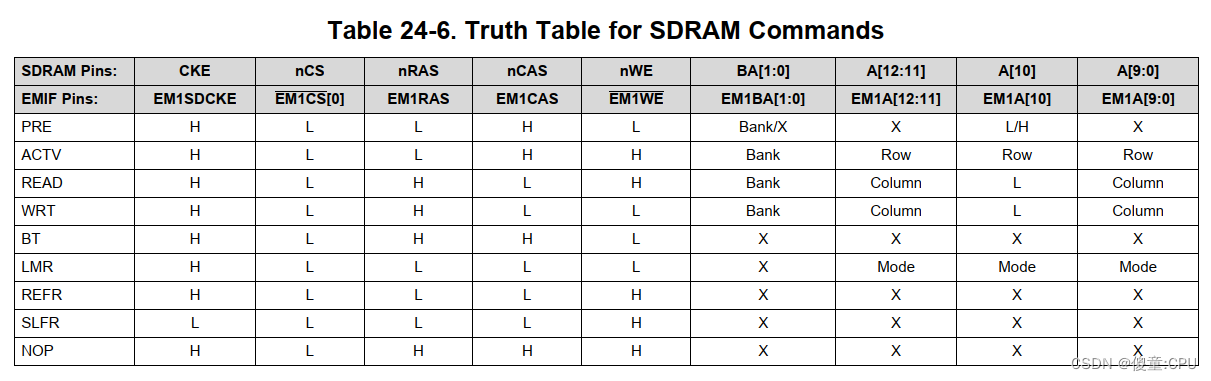

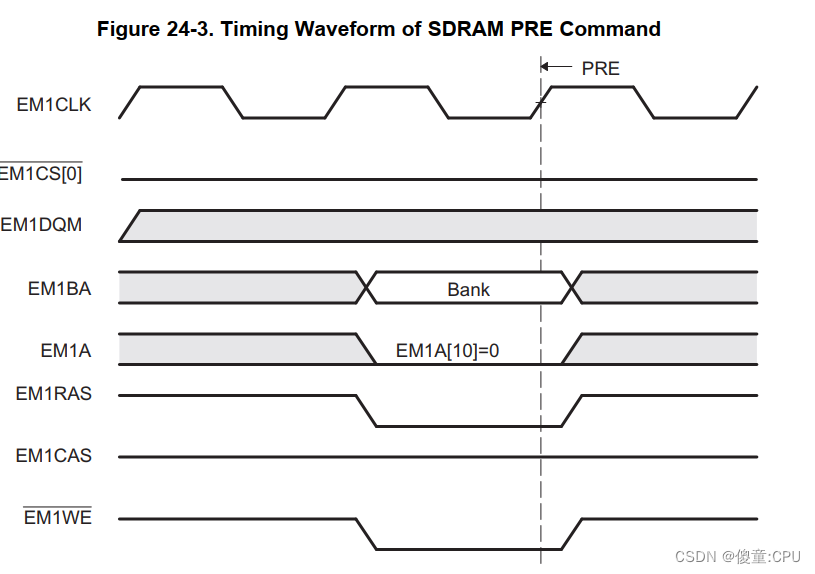

SDRAM命令

EMIF控制器支持表中描述的SDRAM命令。显示了SDRAM命令的真值表,PRE命令的示例时序波形如图所示。在本例中,EM1A[10]被拉低以仅停用EM1BA引脚指定的组。

SDRAM的接口

本文详细介绍了EMIF(外部存储器接口)在支持双核架构设备中的作用,包括其两个独立模块EMIF1和EMIF2的特性,以及与SDRAM和异步设备的兼容性和连接方式。文章重点讨论了EMIF的配置、时钟控制、请求处理机制和与SDRAM的接口技术。

本文详细介绍了EMIF(外部存储器接口)在支持双核架构设备中的作用,包括其两个独立模块EMIF1和EMIF2的特性,以及与SDRAM和异步设备的兼容性和连接方式。文章重点讨论了EMIF的配置、时钟控制、请求处理机制和与SDRAM的接口技术。

2524

2524

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?