写在前面

本文主要对DDR IP核进行相关配置,完成DDR IP核的配置工作。

配置步骤

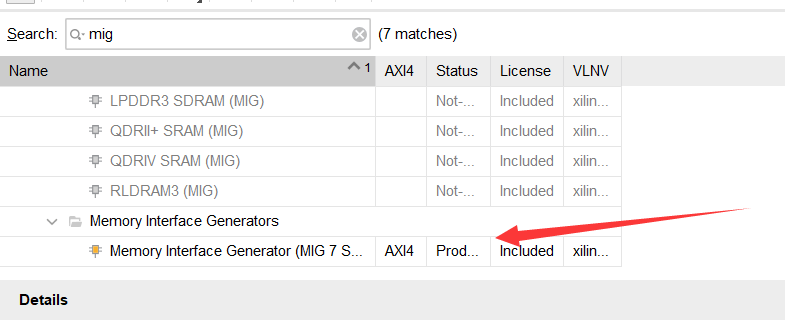

点击 IP Catalog,Search 框中输入 memory interface, 查找到相关的DDR的 IP 核。

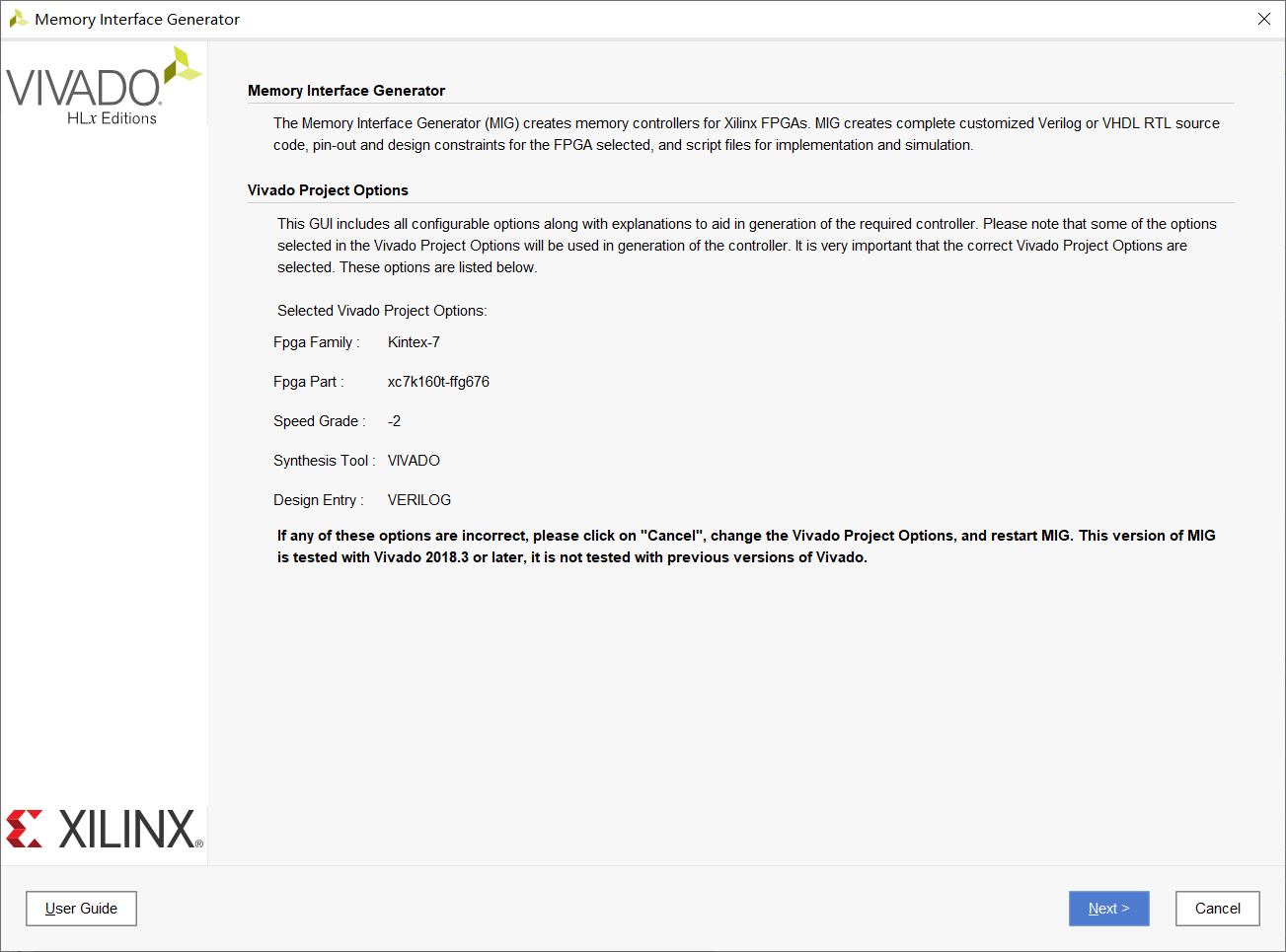

双击 IP 核名称打开 DDR3 SDRAM IP 核调取界面,

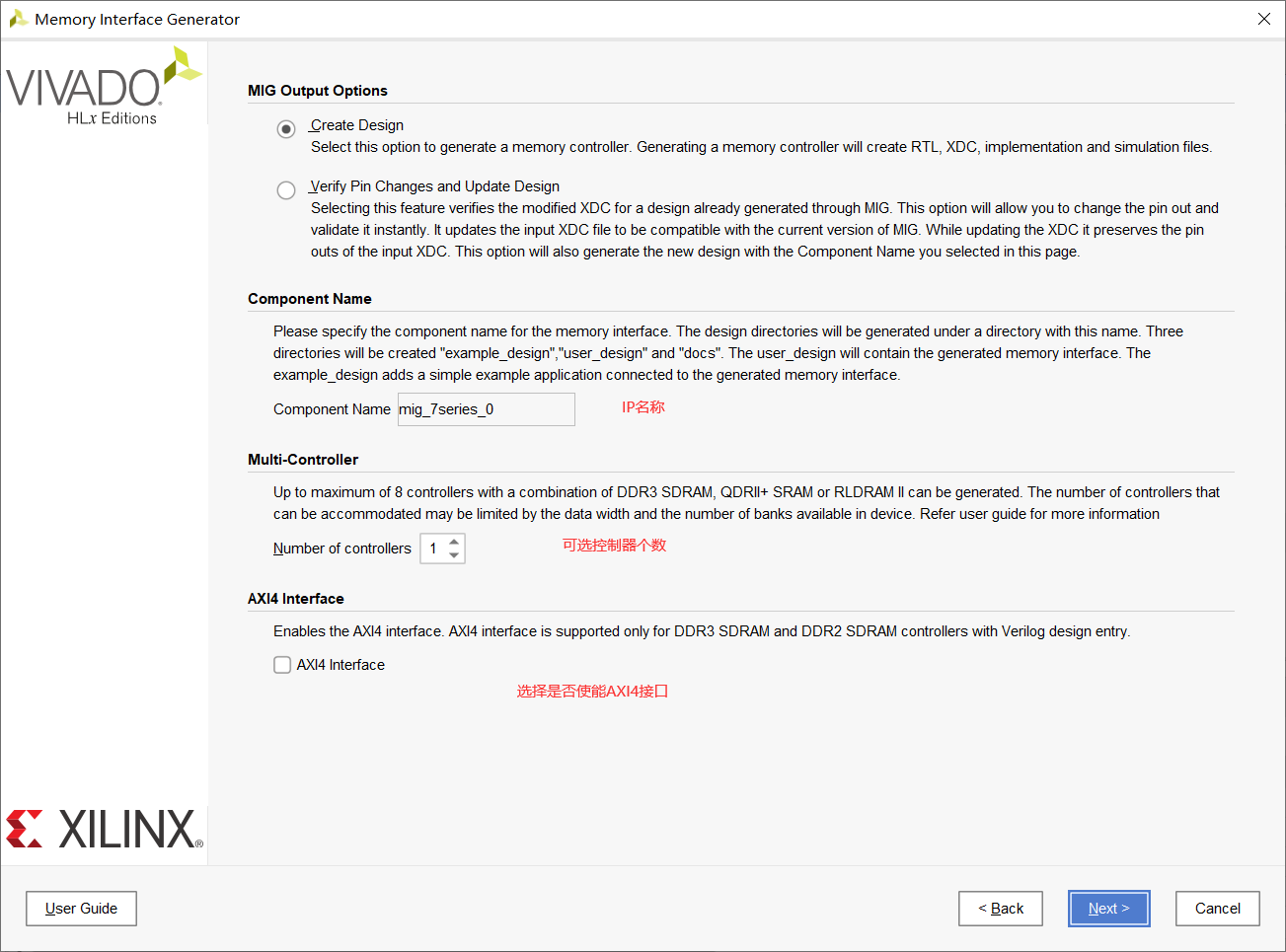

该界面主要是总结了所选芯片的型号等。 点击next,此可以按照个人喜好定义器件的名称,也可以选择 DDR3 控制器的个数,我们的器件名为默认,控制器的数量为1 个 。

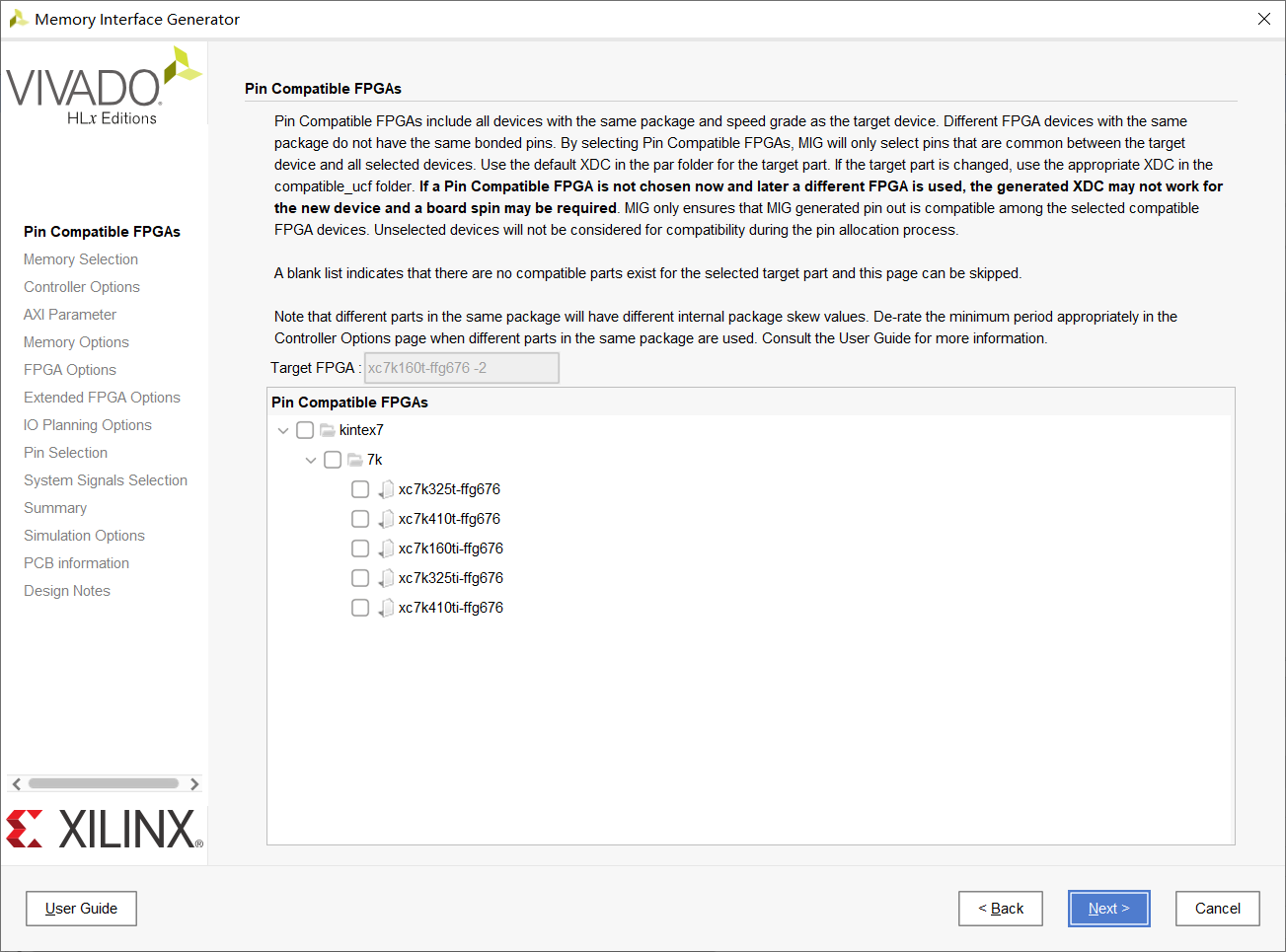

点击 Next,进入到如图所示的界面,如果使用的芯片相同,则可以选择,若没有,可以不选。

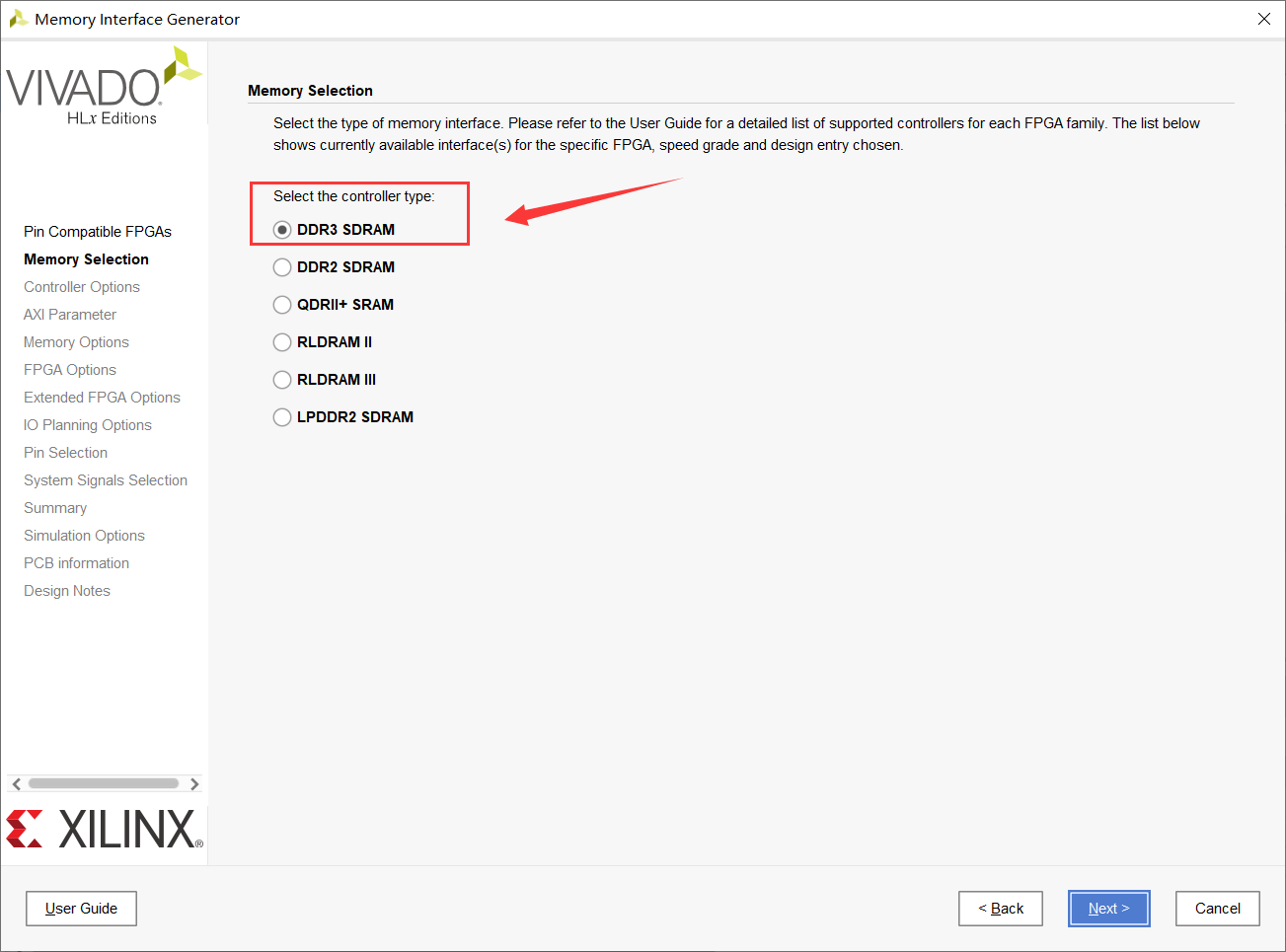

点击下一步, 进入到选取控制器类型的界面, 在此选择 DDR3,所使用的为其他类型的 SDRAM,则可以按照需求选择。

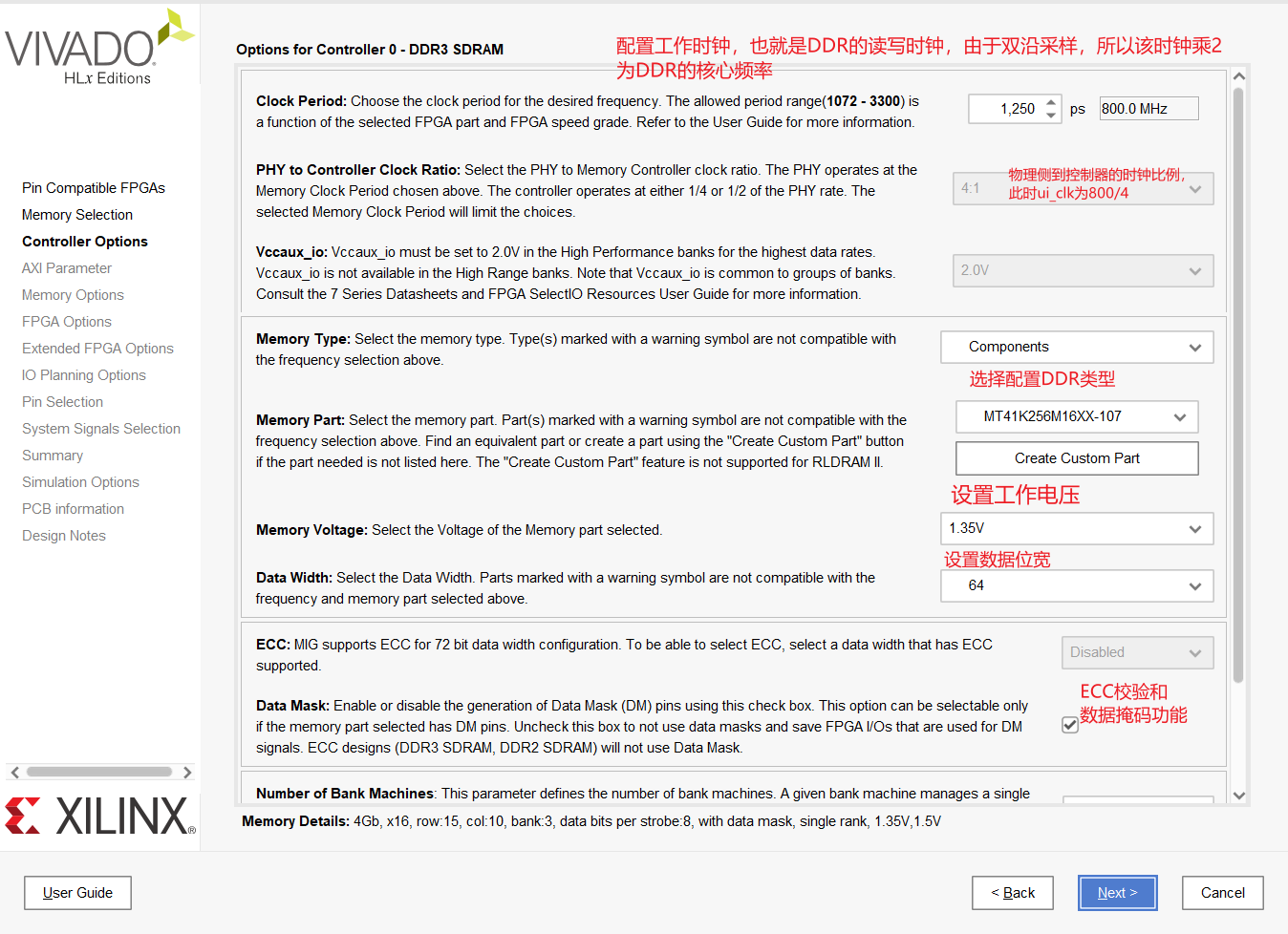

点击 Next,进入到选取 DDR3 SDRAM 相应参数的界面,

选择DDR3 的工作频率,在此设置为 800MHz,若是 FPGA 芯片速度等级不同,则可能工作频率的范围不一样;选择 DDR3 SDRAM 的芯片类型,此处需要根据板卡上的芯片类型来选择,若是列表内没有相应的芯片类型,可以在Create Custom Part 中根据 DDR3 芯片参数来设定; 在此界面设置DDR3 SDRAM 的供电电压为 1.35V,DDR3 SDRAM 数据总线的位宽为64。

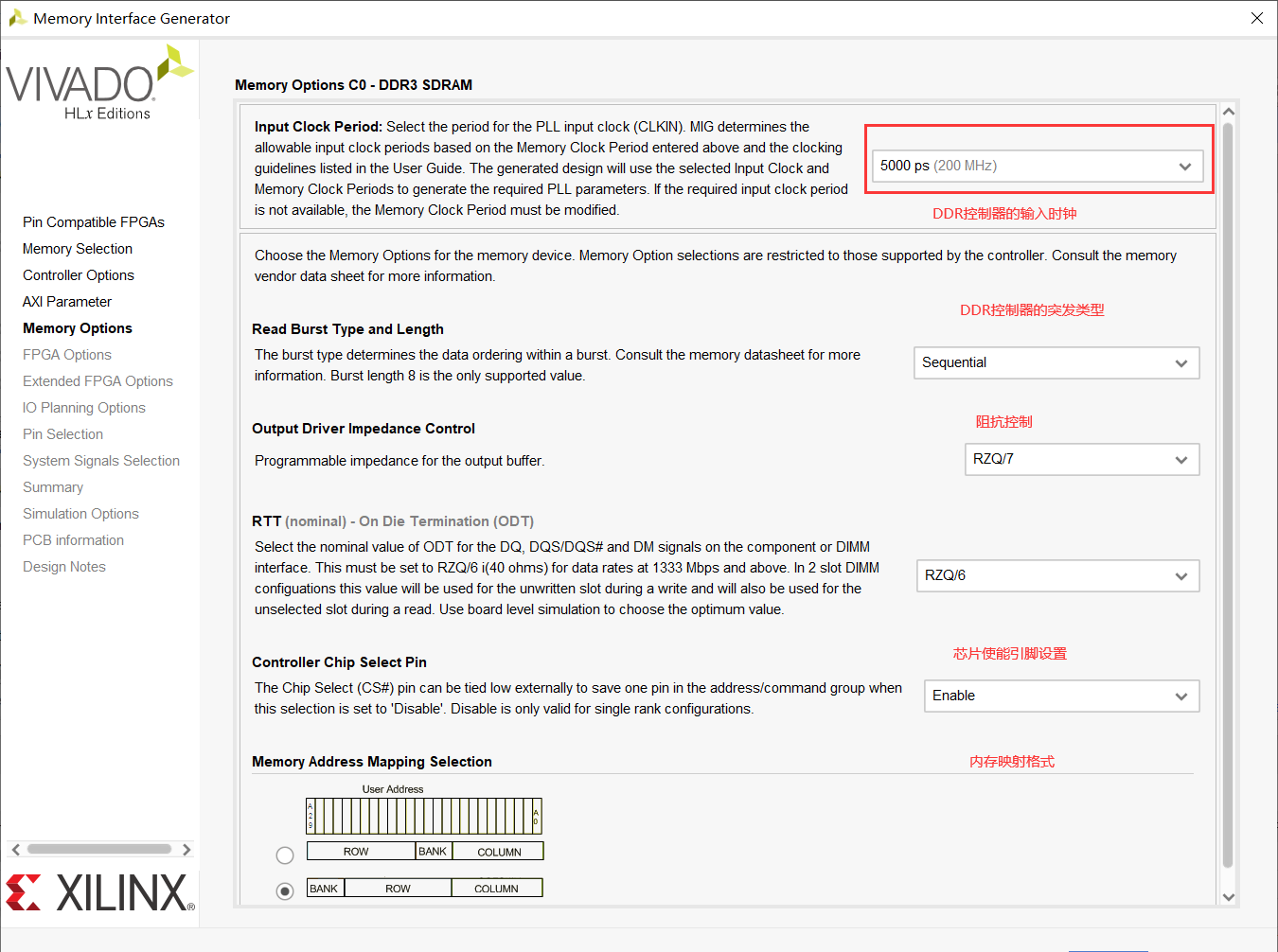

点击 Next,设定 DDR3 控制器的参数。

两种不同的内存地址映射关系,通常对应两种读写操作,第一种通常在读写连续数据使用,第二种通常在读了碎片数据使用。

设定该控制器的输入时钟频率为 200MHz,控制器的突发类型为顺序性,其他默认即可。

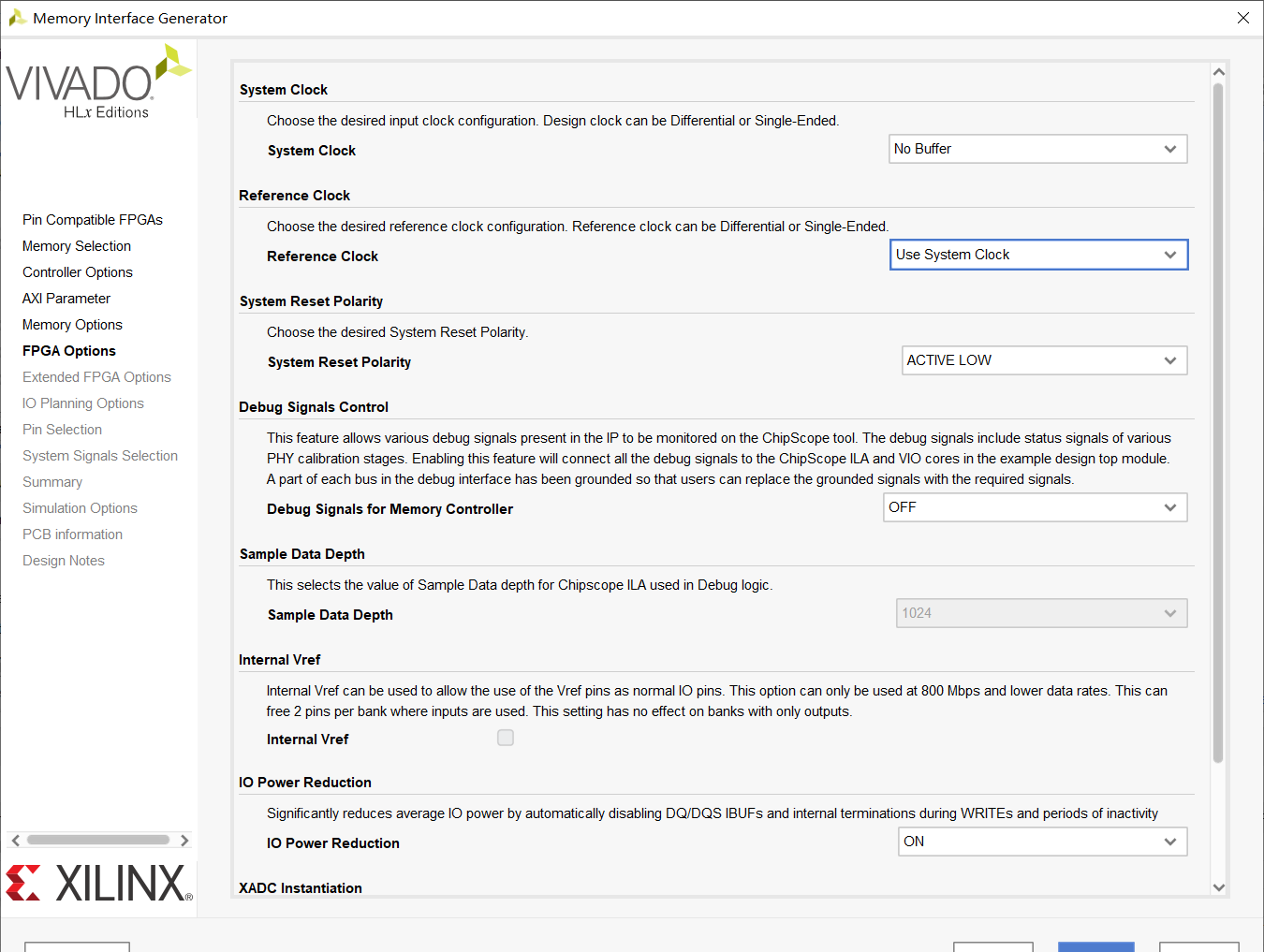

点击 Next, 可以设定系统时钟和参考时钟,

其中系统时钟有 single_ended、deferential 和 no buffer 三种, single_ended 为来源于引脚的单端时钟, deferential为差分时钟, no buffer 为来源于 FPGA 内部的时钟。 参考时钟有四种, 其中三种也为 single_ended、 deferential 和 no buffer, 另外一种为 use system clock,只有在system clock 时钟频率为 199MHZ~201MHz 时, 参考时钟才存在 use system clock选项。

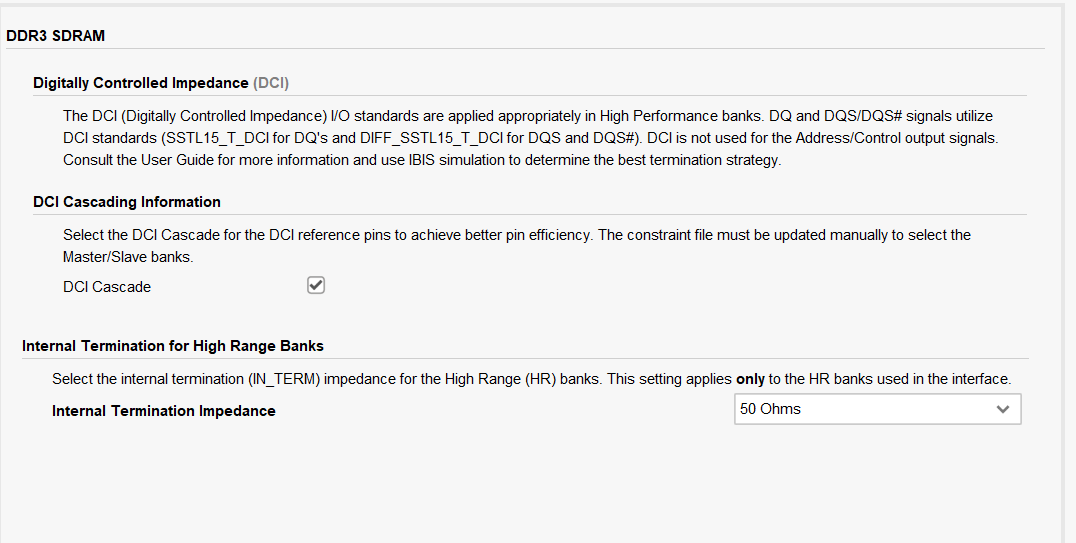

点击 Next 可以进入到设定内部终端电阻的界面,此处可以根据 DDR3 SDRAM芯片手册选择,默认也可。

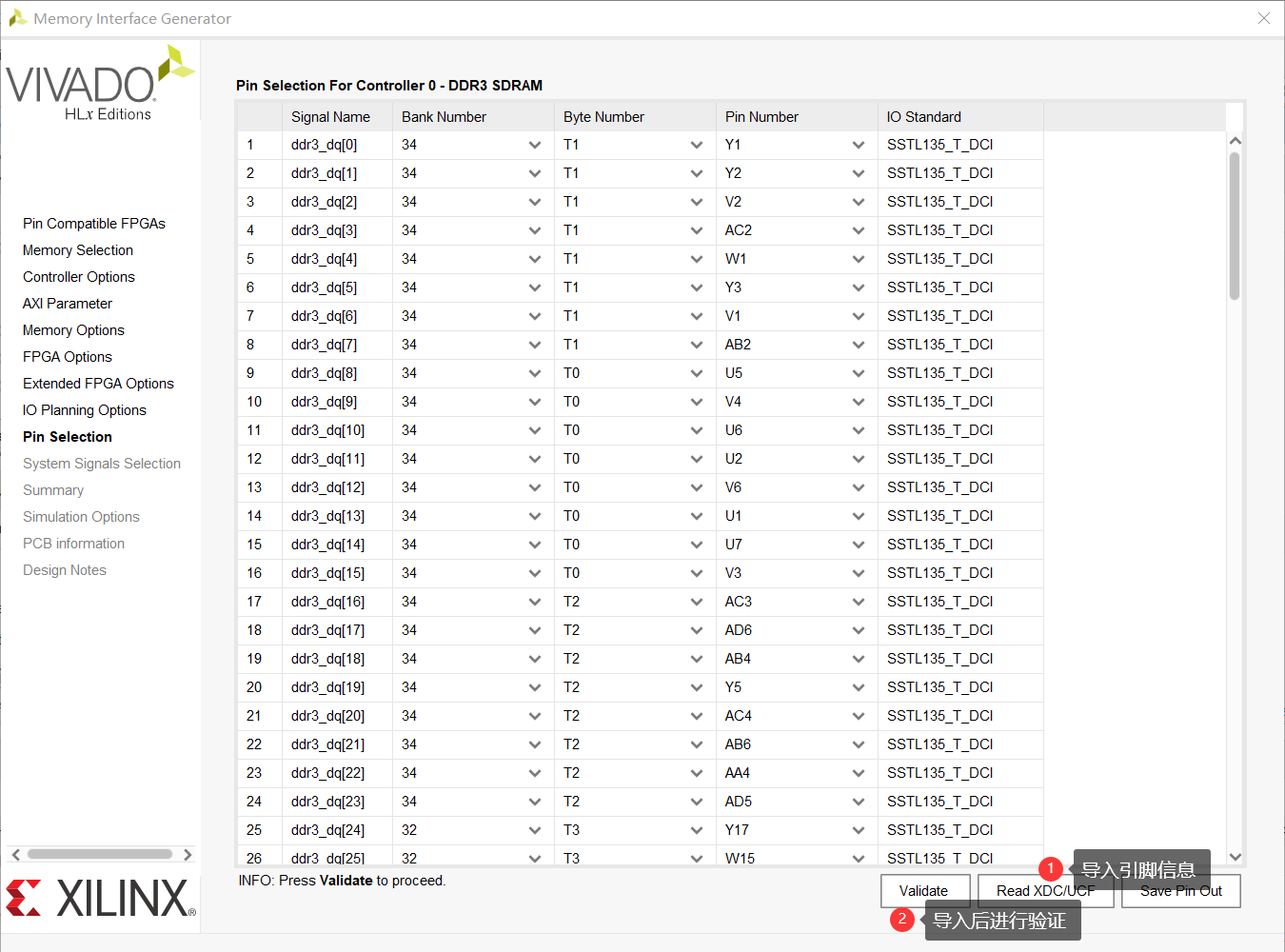

点击 Next,建议勾选第二项,在此可以直接导入 DDR3 SDRAM 的引脚信息,前提是引脚约束文件已经存在,引脚约束文件可以是 UCF 和 XDC 类型。 如果没有相关引脚信息,则需要选择第一项进行新建配置。

点击 Next, 导入相应的约束文件。

选择对应的约束文件,点击打开,之后点击 Validate 来确认约束文件有效。

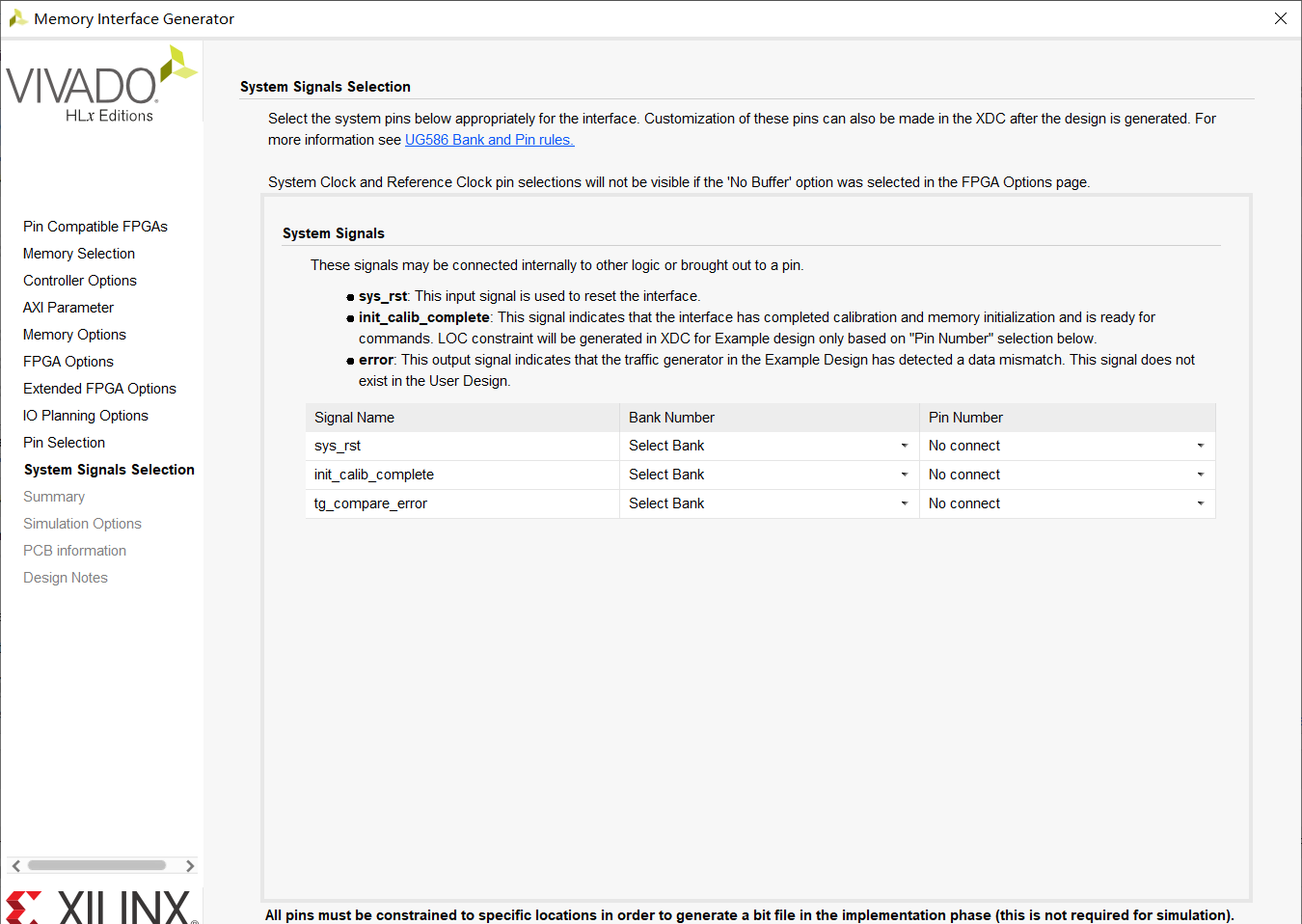

点击 Next, 进入到系统信号配置界面的界面, 此界面中可以按照默认选择。

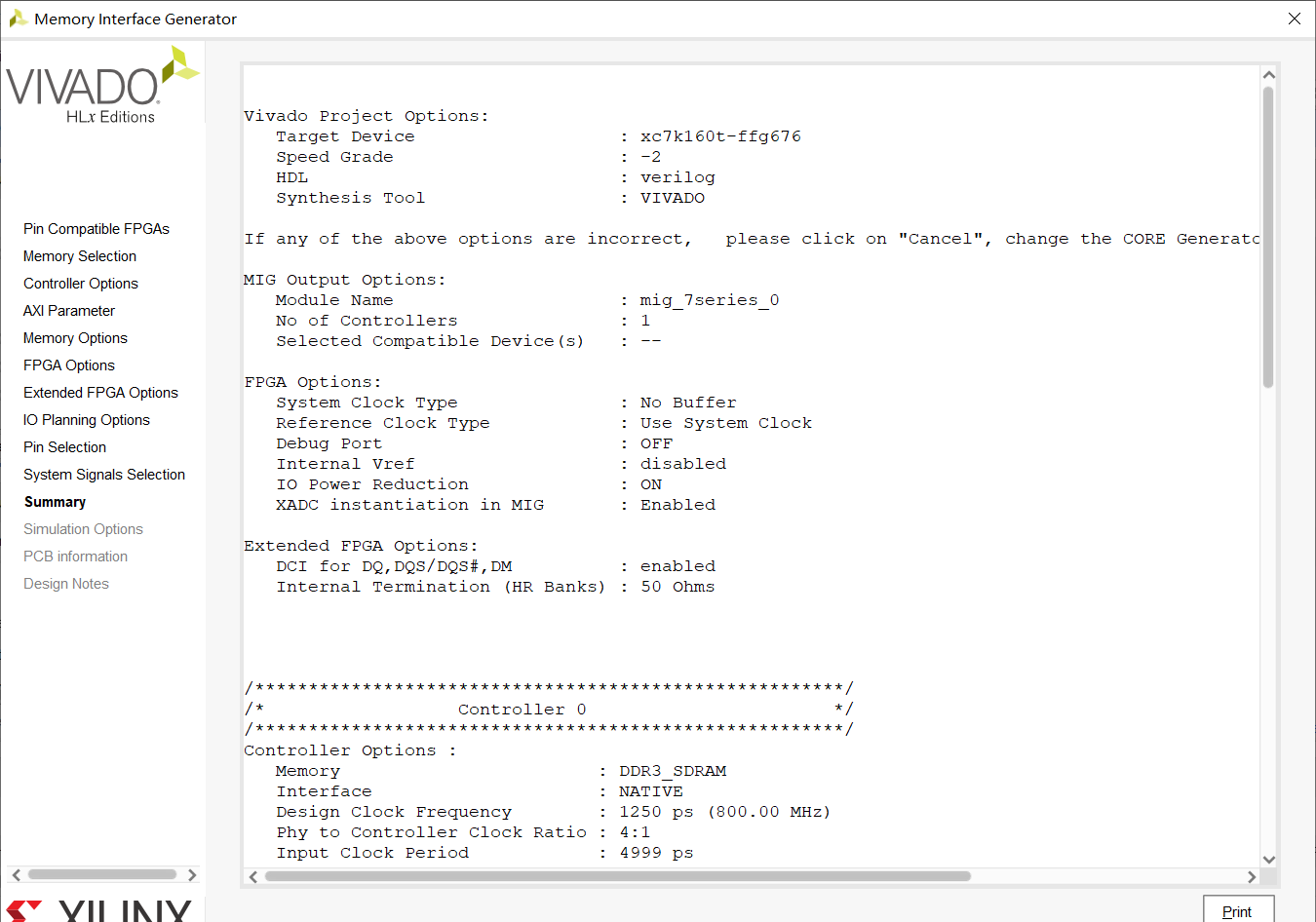

点击 Next,显示对整个创建的 IP 总结。

点击 Next ,选择 Accept,同意生成 DDR3 IP 核仿真模型。 最后点击 Generate,生成 DDR3 IP 核 。

关于带宽计算

理论位宽:PHY时钟 × 双沿采样 × 数据位宽

应用估算位宽 :理论位宽 × 0.8

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?