关于增量编译

所谓增量实现,更严格地讲是增量布局和增量布线。它是在设计改动较小的情形下参考原始设计的布局、布线结果,将其中未改动的模块、引脚和网线等直接复用,而对发生改变的部分重新布局、布线。这样做的好处是显而易见的,即节省运行时间,能提高再次布局、布线结果的可预测性,并有助于时序收敛。

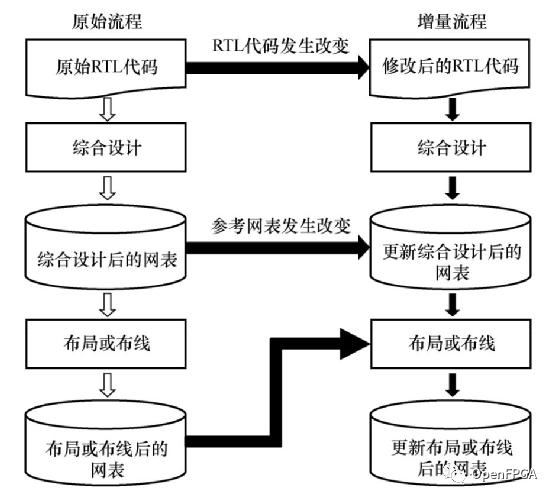

增量实现由两个流程构成:原始流程和增量流程,如图所示。其中,原始流程提供网表。这里的网表可以是布局后的DCP文件,也可以是布线后的DCP文件。

增量实现流程有两种模式:高复用模式和低复用模式。在高复用模式下,布局、布线会尽可能地复用已有布局、布线的结果。在这种情形下,place_design和route_design都只有三种directive可用,分别为Default、Explore和Quick。

以下两种情形适合于高复用模式。

情形1:很小的设计改动。

情形2:与原始设计相比,更新后的设计只是添加了调试模块,如ILA等。

由此可见,高复用模式在网表时序收敛且多达95%的逻辑单元被复用时最为有效。

与高复用模式相比,低复用模式则适用于更新后的设计与参考设计相比有较大的改动,或者用户通过read_checkpoint的选项−reuse_objects指定复用逻辑单元的情况。此时,place_design和route_design的所有−directive均可用。

当布局、布线在某些区域面临挑战时,低复用模式更为有效。例如,从网表中获得较好的Block RAM和DSP的布局,或者时序难以收敛的逻辑单元。这些都可通过Tcl命令获得。

一般来说,增量编译都是与设计锁定联合使用的。

设计锁定与增量编译方法

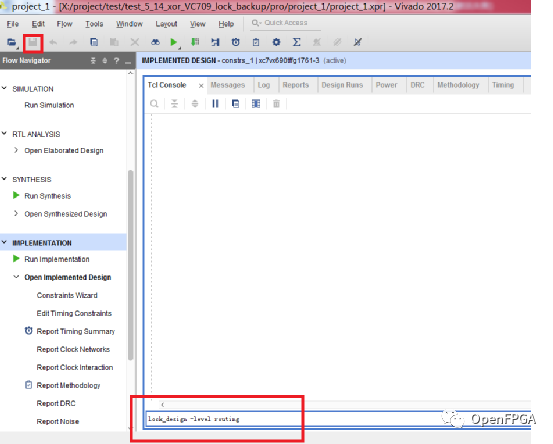

为了实现对模块的布局(place)、布线(route)的锁定,仅适用增量编译是不够的,因为增量编译的本质目的是为了实现编译时间的缩短,还需要引入设计锁定,设计锁定的TCL命令是:lock_design –level routing

下面例说操作方法。

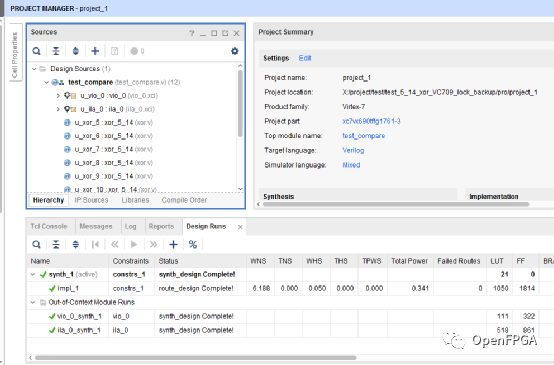

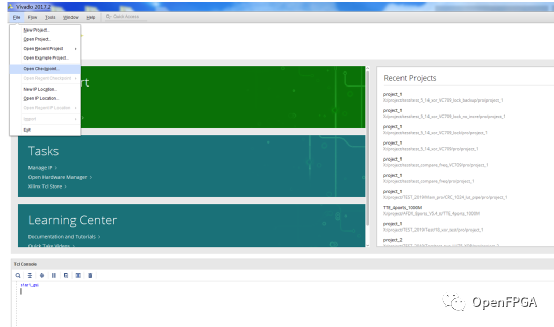

(1)建立工程:建立一个工程,走完综合实现的流程,如图1所示,该工程将作为样例工程(工程名:incre_compile_demo),将该工程备份一份(工程名:initial_project,后面对比要用到这个工程);

图1 建好的工程

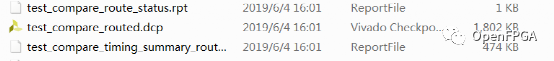

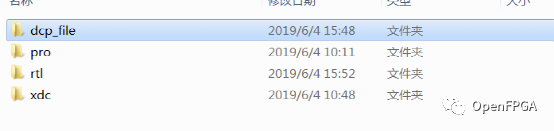

(2)找到dcp文件:增量编译需要有一个参考文件,这个参考文件是“参考设计”实现之后生成的,后缀是“.dcp”,该文件的路径一般在“..\ project_1\project_1.runs\impl_1”路径下,如图2所示,新建一个文件夹(名字是dcp_file),将该文件复制到其中,如图3所示;

图2 dcp文件

图3新建文件夹,复制dcp文件

(3)锁定设计:前面说道,简单的增量编译是不能保证模块固定在某个位置的,为了实现这一点,需要对设计进行锁定,方法是,打开一个新的Vivado界面,然后打开dcp_file文件夹下的dcp文件(注意选择“open checkpoint”),如图4所示;打开后,在TCL Console中输入命令:“lock_design –level routing”,点击左上角保存,如图5所示,做完这一步后,设计就锁定好了,dcp文件就可以用了;

图4 vivado打开dcp界面

图5 锁定设计并保存

(4)增量编译:

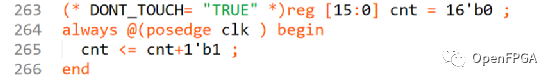

1)修改代码,将顶层模块(test_compare.v)line263-line266注释取消,保存,如图6所示;

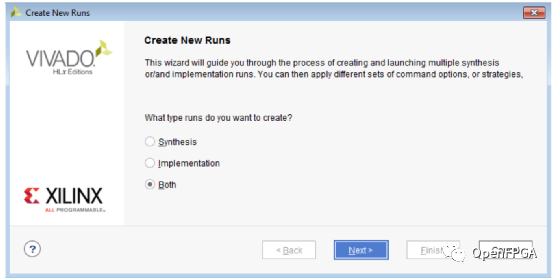

2)在主界面菜单栏处,点:Flow > Create Runs;

3)选both,点next,如图7所示;

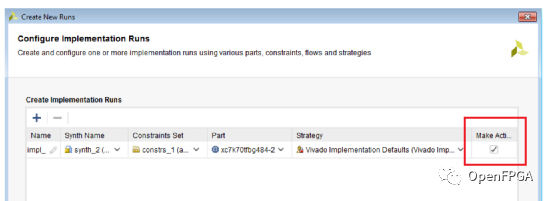

4)勾选make active,点next,如图8所示;

5)选Do not launch now,点next,如图9所示;

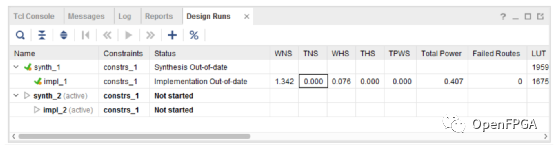

6)完成后如图10所示;

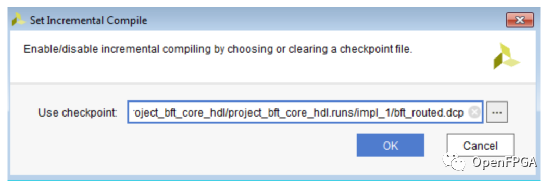

7)在impl_2右键,选择“Set Incremental Compile”,选择步骤(3)中准备好的dcp文件,示意图如图11所示(注意这只是一个示意图,图中选的文件不是步骤(3)准备好的那个文件)

8)开始综合、实现,完成增量编译过程。

图6 改代码

图7 选both

图8 make active

图9 Do not launch now

图10 新的run已建好

图11 选择参考dcp文件

3、正确性验证

怎么证明增量编译后,原始设计成功锁定了呢?我们来做一个对照实验。

样本1:原始工程,名称是: initial_project;

样本2:增量编译工程,名称是: incre_compile_demo;

样本3:原始工程复制一份出来,不进行增量编译,直接修改代码(见图6),重新综合实现,名称是:modify_project。

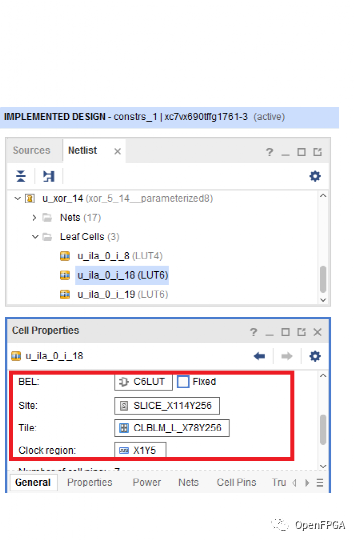

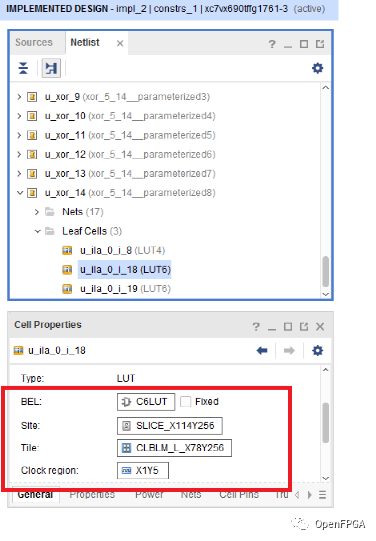

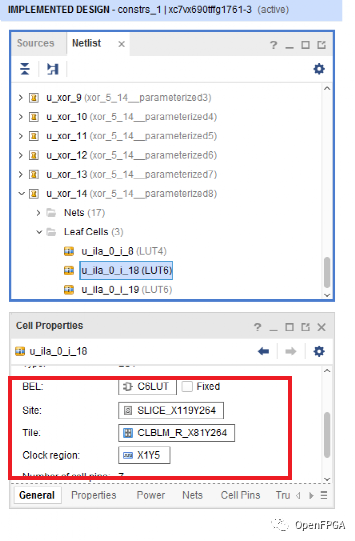

打开三个工程,之后open implemented design,选取几个模块,观察其在FPGA上的位置,发现样本1和样本2位置完全一样,而样本3和前两个样本不一样,说明设计锁定是成功的,如图12、13、14所示。

图12 样本1位置观察

图13 样本2位置观察

图14 样本3位置观察

Vivado下如何锁定设计的模块的布局布线

Xilinx官方论坛上也有相关问题的回答。

https://forums.xilinx.com/t5/Vivado/Vivado%E4%B8%8B%E5%A6%82%E4%BD%95%E9%94%81%E5%AE%9A%E8%AE%BE%E8%AE%A1%E6%A8%A1%E5%9D%97%E7%9A%84%E5%B8%83%E5%B1%80%E5%B8%83%E7%BA%BF/td-p/885693。

Vivado下如何锁定设计模块的布局布线

问题:

我现在设计了一个延时模块,应用后需要把该模块的布局和布线全部锁定,然后在别的项目中直接调用。现在布局没有问题。可以通过约束文件来锁定,就是布线不能大范围锁定,否则应用时会失败。我已经尝试过增量编译(调用DCP文件)的功能,发现在增量编译中布局布线并不是全部不变的,个别走线也是会变的。请问有办法把布线也固定下来吗?(Tool: Vivado17.3 Device: K7)

回答1:如果你用的是Ultrascale/Ultrascale+ , 我觉得PR是个不错的选择,你的目标模块可以放在静态部分,只占据很小的一块面积,剩下大块的动态部分.但是7系列有很多primitive不能放在动态,静态的部分包含的逻辑过多,剩下供你修改的逻辑偏少,不太适合目前的应用场景.

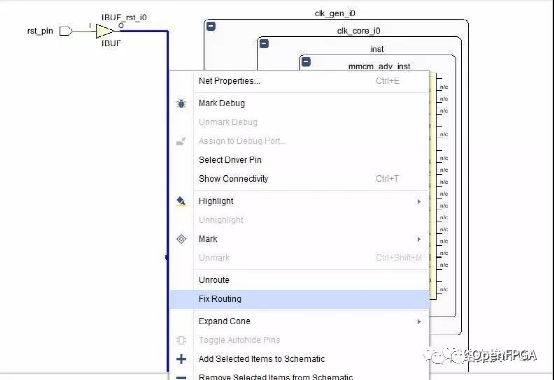

回答2:关于锁定某一个net的布线路径,请参考以下步骤:

1.打开跑完布局布线的工程,Open Implemented Design

2.找到你要锁定布线的net,选中,右键菜单点击Fixed Routing,如下图所示:

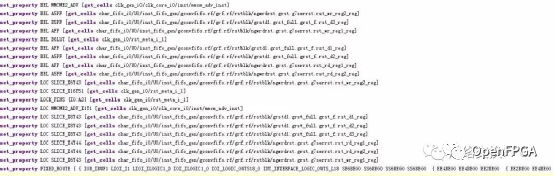

3. Tcl Console里面会打印出一些命令,然后在Tcl Console里面敲命令:write_xdc/dirt.xdc

4. 打开导出的xdc,在最下面的部分会有所有元件的位置锁定以及FIXED_ROUTE,示例如下:

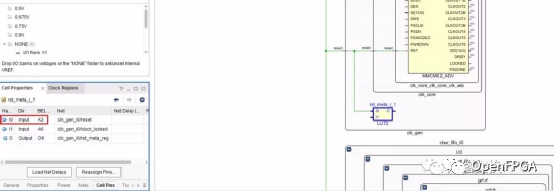

5. 另外还需注意的是,负载中有LUT的话需要将LUT的输入pin也锁住。以下图的LUT2为例,在其property窗口中找到Cell pins,信号是连到LUT2的I0端,映射到BEL pin是A3。

因此上述导出的位置锁定约束中还有一个LOCK_PINS的设置:

set_property LOCK_PINS {I0:A3} [get_cells clk_gen_i0/rst_meta_i_1]

6. 将这部分有关锁定的约束拷贝到你工程的约束文件中,重新跑implementation,这条线会按照原先的结果布。

温馨提示:

我们并不建议完全锁死某个模块的所有布线,当合入的工程比较复杂,用到的布线资源较密集时,工具没有灵活性去调整和优化,有很大的概率会布线失败。

划分静态区和动态区

除了上述的逻辑锁定方法之外,Xilinx 的FPGA还提供了静态区和动态区的划分也可以实现逻辑的锁定。只不过静态区占据了大多数的空间,动态区是可以随意修改的小部分空间。

FPGA提供了现场编程和重新编程的灵活性,无需通过改进的设计进行重新制造。部分重配置(PR)进一步提高了这种灵活性,允许通过加载部分配置文件(通常是部分BIT文件)来修改操作FPGA设计。在完整的BIT文件配置FPGA之后,可以下载部分BIT文件以修改FPGA中的可重配置区域,而不会影响在未重新配置的设备部分上运行的应用程序的完整性。

部分可重构的基本前提

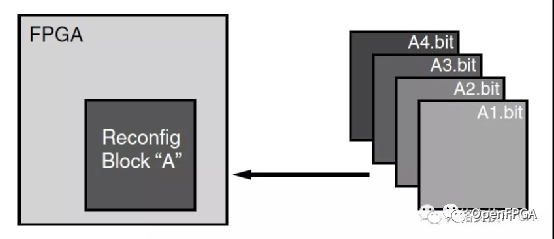

如图所示,通过下载几个部分BIT文件A1.bit,A2.bit,A3.bit或A4.bit中的一个来修改在重新配置块A中实现的功能。FPGA设计中的逻辑分为两种不同的类型,可重构逻辑和静态逻辑。FPGA块的灰色区域表示静态逻辑,标记为Reconfig Block“A”的块部分表示可重配置逻辑。静态逻辑仍然有效,并且不受加载部分BIT文件的影响。可重配置逻辑由部分BIT文件的内容替换。

为什么在单个FPGA器件上动态地对多个硬件进行时间复用的能力是有利的。这些包括:

•减小实现给定功能所需的FPGA器件尺寸,从而降低成本和功耗

•为应用可用的算法或协议选择提供灵活性

•实现设计安全性的新技术

•提高FPGA容错能力

•加速可配置计算

除了减小尺寸,重量,功耗和成本之外,部分重配置还可以实现没有它的新型FPGA设计。

414

414

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?