一个数能够开根号的前提是,其全部因子,必须成对出现(偶数次),而不可以是奇数次。

- 一个偶数如果能够开根号(是偶数,则存在 2 的因子,因为能够开根,则其因子需成对出现),则其开根号的结果一定也是偶数;

- 一个奇数如果能够开根号(不存在 2 ),则其开根号的结果一定也是奇数;

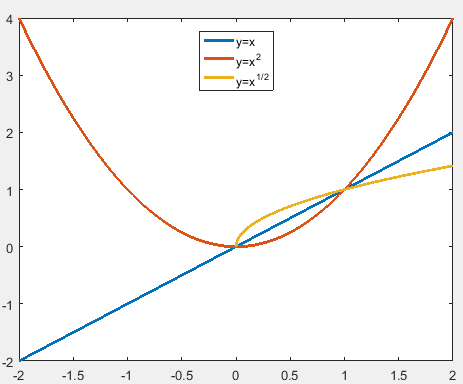

1. y=x2 与 y=x√

首先二者互为反函数,又因为 x√ 的定义域限制,可得 y=x2 与 y=x√ 在第一象限关于 y=x 对称。

- x√≥x ⇒ 0≤x≤1

- 1<a<2 ,对其无论开多少次根号, a12k 其值都会大于 1,而不会小于 1;

y=x , y=x2 , y=x√ ,三条线的关系如下图所示:

7887

7887

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?