4 DDR5 SDRAM命令描述和操作-36

4.36 DDR5 ECC透明度和错误清除

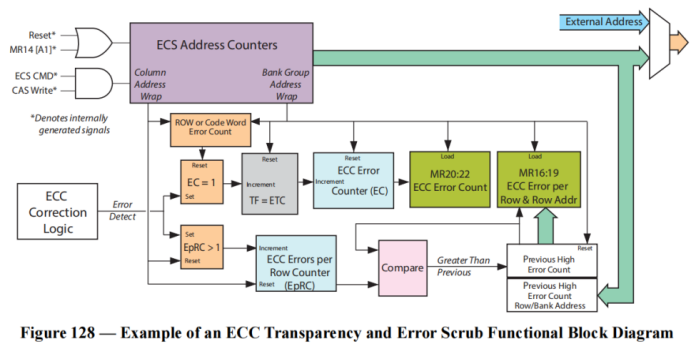

DDR5 ECC透明度和错误清除通过具有错误计数方案的ECC错误检查和清除(ECS)模式,实现了透明度。ECS模式允许DRAM在内部读取、纠正单比特错误,并将纠正后的数据位写回阵列(清除错误),同时提供错误计数的透明度。建议至少每24小时对DRAM进行一次完全错误清除。

有两种ECS模式可供选择,通过模式寄存器进行设置。手动ECS模式(MR14:OP[7] = 1B)通过多功能命令允许进行ECS操作。自动ECS模式(MR14:OP[7] = 0B,默认设置)允许ECS在DRAM内部运行。

ECS功能在所有设备配置上都可用。

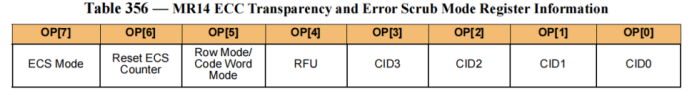

ECS模式实现了两个计数器,用于跟踪在操作过程中检测到的ECC码字错误:错误计数器(EC)和每行错误计数器(EpRC)。EC默认计算具有错误的行数;然而,它也可以配置为计算具有错误的码字数。在行模式(默认模式)下,EC跟踪至少有一个码字错误的行数,受阈值过滤器限制。在码字模式下,EC跟踪码字错误的总数,同样受阈值过滤器限制。第二个计数器EpRC跟踪具有最大码字错误数量的行的错误计数,以及该行的地址。EpRC错误报告也受到单独的阈值过滤器的限制。ECS模式操作的通用功能块示例如图128所示,而ECC错误检查和清除模式的模式寄存器(MR14)如表356所示。

4.36.1 ECS模式操作之前的模式寄存器和DRAM初始化

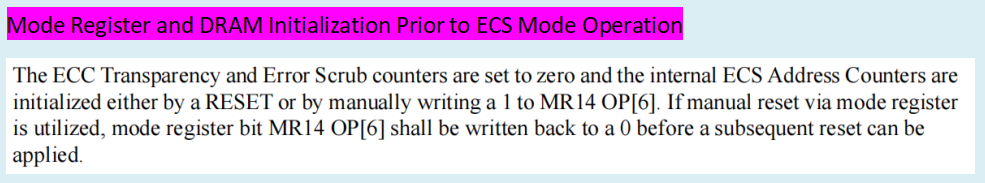

ECC透明度和错误清除计数器被设置为零,并且内部的ECS地址计数器可以通过RESET或手动将1写入MR14 OP[6]来初始化。如果使用模式寄存器进行手动复位,则在应用后续复位之前,必须将模式寄存器位MR14 OP[6]写回为0。

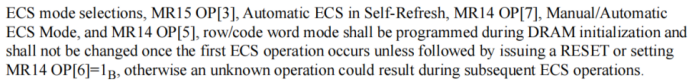

在DRAM初始化过程中,应进行ECS模式选择的编程,其中包括MR15 OP[3]自刷新中的自动ECS模式、MR14 OP[7]手动/自动ECS模式和MR14 OP[5]行/码字模式,并且在第一次ECS操作发生后,除非进行RESET或设置MR14 OP[6]=1B,否则不应更改这些设置,否则在后续的ECS操作中可能会导致未知的操作。

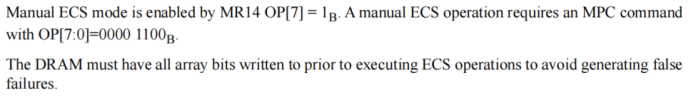

通过将MR14 OP[7]设置为1B可以启用手动ECS模式。手动ECS操作需要使用OP[7:0]=0000 1100B的MPC命令。

在执行ECS操作之前,必须将DRAM的所有阵列位写入,以避免生成虚假错误。

4.36.2 ECS操作

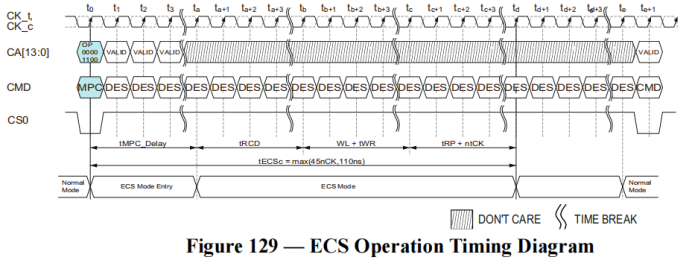

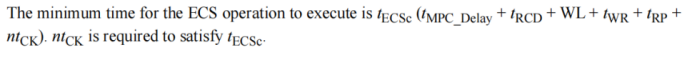

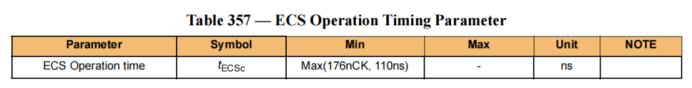

在执行手动ECS操作之前,所有bank都应该被预充电并处于空闲状态。

执行手动ECS操作,使用OP[7:0]=0000 1100B的MPC命令,会生成以下内部自定时命令序列:ACT→RD→WR→PRE。ECS操作的时序如图129所示。

在执行手动ECS操作时,DQ保持在RTT_PARK状态,而DQS保持在DQS_RTT_PARK状态。除了tECSc期间的DES命令外,手动ECS操作只允许使用ODT NT命令,这些命令可能会改变DQ和DQS的终端状态。

任何非法使用手动ECS模式的情况(例如,刷新或温度违规)将导致操作不被保证。

通过使用OP[7:0]=0000 1100B的MPC命令执行手动ECS操作,将根据内部ECS地址计数器的行地址,在MPC命令后的tMPC_Delay时间内发出一个内部定时的ACT命令进行行激活。ACT命令后应紧接着一个延迟时间tRCD的WR命令。WR命令将根据内部ECS地址计数器的列地址对确定的编码字进行内部的读-修改-写操作。

内部的读-修改-写操作将会:

1. 从数组中读取整个编码字(128个数据位和8个校验位)。

2. 如果检测到错误,则纠正编码字或校验位中的单个位错误。

3. 将结果编码字写回DRAM阵列。

WR命令后面是一个延迟时间WL + tWR的PRE命令。PRE命令将自动重新启用DRAM的I/O和地址输入,并在满足tECSc后的延迟时间tRP + ntCK后将DRAM返回到空闲模式。

对于每个ECS操作,ECS地址计数器在每次内部ECS WR命令之后递增列地址,以选择下一个编码字和校验位。一旦列计数器回绕(访问完行上的所有编码字和校验位),行计数器将递增,直到访问完银行内的每一行的编码字。当行计数器回绕(访问完银行内的所有行),银行计数器将递增,而银行组内的下一个银行将重复访问每个编码字的过程。当银行计数器回绕时,银行组计数器递增,下一个银行组将重复访问每个编码字的过程,直到访问完DRAM内的所有银行组。

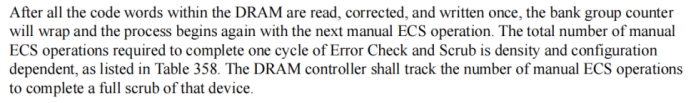

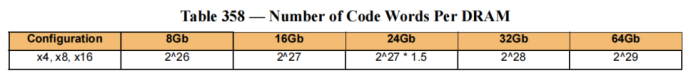

在所有DRAM内的编码字被读取、纠正和写入一次后,银行组计数器将回绕,并且下一个手动ECS操作将重新开始。完成一次错误检查和清除周期所需的手动ECS操作总数取决于存储密度和配置,可参考第358表。DRAM控制器应跟踪完成设备全面清除所需的手动ECS操作次数。

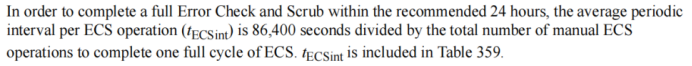

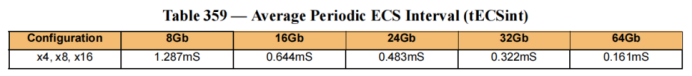

为了在推荐的 24 小时内完成完整的错误检查和清除操作,平均周期间隔的每次 ECS 操作(tECSint)等于 86,400 秒除以完成一次完整 ECS 周期所需的手动 ECS 操作的总数。tECSint 在表 359 中包含。

为了让 DDR5 SDRAM 在自动 ECS 模式下执行自动 ECS 操作,主机需要定期发出 REFab 命令或定期进入自刷新模式。在推荐的 24 小时内完成自动清除操作所需的 DRAM 的 REFab 命令或自刷新进入之间的最大间隔为 tECSint。满足 REFab/自刷新要求可以使 DRAM 在自动 ECS 模式下执行自动 ECS 操作时无需对刷新模式使用进行额外限制,即在自动 ECS 模式下可以使用所有 bank/同一 bank 刷新或正常/FGR 模式刷新。 DRAM 需要自动执行的 REFab 命令(每个 tECSint 发送一个)多于 ECS 操作所需的数量时,DRAM 可以将其用于正常刷新操作。发出多个 REF 命令的操作不得超过一个 1 x tREFI 窗口允许的总数,如规范的刷新操作调度灵活性部分所述。

在自动 ECS 模式下,ECS 命令和时序由 DRAM 内部生成和满足,遵循平均周期性 ECS 间隔时序,以确保错误检查和清除操作在推荐的 24 小时内完成,并更新透明寄存器(MR16-20)。

如果通过 MR14 OP[7]=0B 启用了自动 ECS,或者通过 MR15 OP[3]=1B 启用了自刷新中的自动 ECS,DRAM 需要在自刷新模式下执行自动 ECS 操作,以满足平均周期性 ECS 间隔时序。然而,在自刷新模式下,DRAM 的清除速率可能会有一些变化,因为 DRAM 需要将内部操作与内部振荡器频率同步。进入和退出自刷新不会重置 ECS 透明计数器/寄存器。允许在 REFab 命令之间或另一个自刷新进入之间的最大间隔的间隔时序在退出自刷新后可以重新开始。

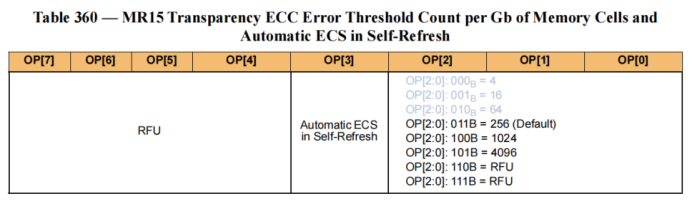

ECC 透明度和错误清除方案包括一个用户可编程的 ECS 阈值过滤器,该过滤器屏蔽小于编程过滤器值的错误计数。使用 MR15 设置该值,如表 360 中所列。默认的 MR15 设置是每 Gb 存储单元 256 次失败(OP[2:0] = 011B)。

一旦超过了纠错错误阈值计数(ETC),纠错错误计数器(EC)开始跟踪。EC的值会根据第4.36.3节中描述的方式被传输到模式寄存器MR20中。每行纠错计数器(EpRC)的错误信息也会在超过ETC之后,根据第4.36.3节中描述的方式被传输到模式寄存器MR16:19中。

4.36.3 ECS错误追踪

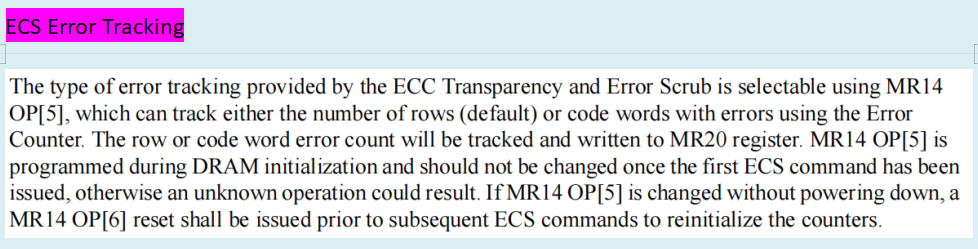

使用ECC透明度和错误清除提供的错误跟踪类型可以通过MR14 OP[5]进行选择,它可以跟踪行数(默认)或使用错误计数器跟踪具有错误的码字。行或码字错误计数将会被跟踪并写入MR20寄存器。MR14 OP[5]在DRAM初始化过程中进行编程,并且在发出第一个ECS命令之后不应更改,否则可能导致未知操作。如果在不关机的情况下更改了MR14 OP[5],则在后续的ECS命令之前必须发出MR14 OP[6]复位以重新初始化计数器。

当选择了ECC行计数模式时,每次检测到带有检验位错误的行时,错误计数器(EC)会递增。在所有银行组的所有银行中执行ECS操作后,错误计数器的结果将被加载到MR20中,并进行错误阈值报告。传输到模式寄存器后,EC将被复位。

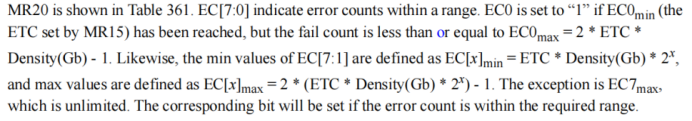

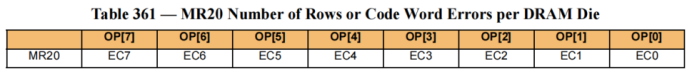

MR20在表361中显示。EC[7:0]表示错误计数的范围。如果错误计数达到了EC0min(由MR15设置的ETC),但失败计数小于或等于EC0max = 2 * ETC * Density(Gb) - 1,那么EC0将设置为“1”。同样,EC[7:1]的最小值被定义为EC[x]min = ETC * Density(Gb) * 2x,最大值被定义为EC[x]max = 2 * (ETC * Density(Gb) * 2x) - 1。例外是EC7max,它是无限制的。如果错误计数在所需范围内,相应的位将被设置。

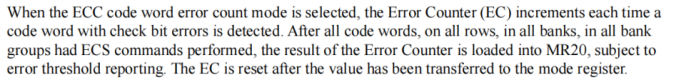

当选择ECC码字错误计数模式时,每次检测到带有校验位错误的码字时,错误计数器(EC)都会递增。在对所有存储器芯片中的所有bank中的所有行执行了ECS命令之后,错误计数器的结果将加载到MR20中,并进行错误阈值报告。在将该值传输到模式寄存器后,错误计数器将被重置。

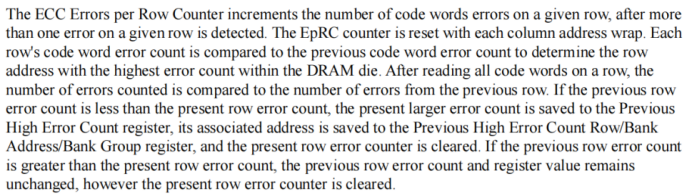

ECC行错误计数器会在检测到给定行上出现多个错误时递增该行上的码字错误数。每次列地址换行时,EpRC计数器将被重置。将每一行的码字错误计数与前一行的码字错误计数进行比较,以确定DRAM芯片中错误计数最高的行地址。在读取完一行上的所有码字后,将计算出的错误数与前一行的错误数进行比较。如果前一行的错误计数小于当前行的错误计数,则将较大的错误计数保存到Previous High Error Count寄存器中,并将其相应的地址保存到Previous High Error Count Row/Bank Address/Bank Group寄存器中,同时清除当前行的错误计数器。如果前一行的错误计数大于当前行的错误计数,则前一行的错误计数和寄存器值保持不变,但当前行的错误计数器被清除。

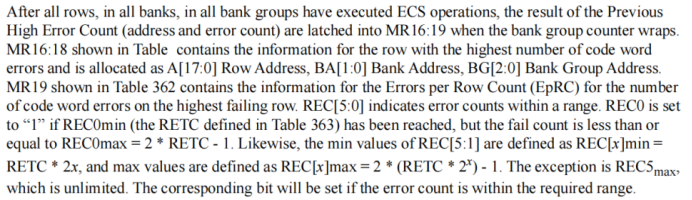

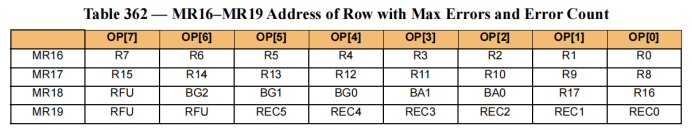

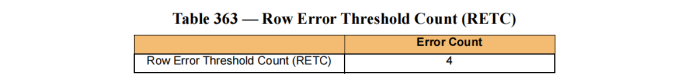

在所有行,所有bank和所有bank组执行ECS操作之后,当bank组计数器换行时,Previous High Error Count(地址和错误计数)的结果被锁存到MR16:19中。表中显示的MR16:18包含了具有最多码字错误的行的信息,并分配为A[17:0]行地址,BA[1:0]bank地址和BG[2:0]bank组地址。表格362中显示的MR19包含了拥有最高失败行上的码字错误数(EpRC)的信息。REC[5:0]表示一个范围内的错误计数。如果达到了REC0min(在表363中定义的RETC),但失败计数小于或等于REC0max = 2 * RETC - 1,则REC0将被设置为“1”。同样,REC[5:1]的最小值定义为REC[x]min = RETC * 2x,最大值定义为REC[x]max = 2 * (RETC * 2x) - 1。异常情况是REC5max,它是无限制的。如果错误计数在所需范围内,则相应的位将被设置。

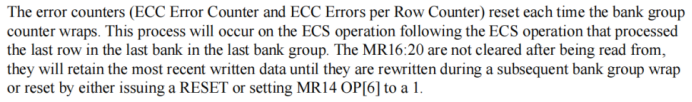

错误计数器(ECC错误计数器和每行的ECC错误计数器)在bank组计数器换行时会被重置。这个过程将在处理最后一个bank组中最后一个bank中的最后一行的ECS操作之后的ECS操作中发生。MR16:20在读取后不会被清除,它们将保留最近写入的数据,直到在后续的bank组换行期间被重新写入,或者通过发出RESET命令或将MR14 OP[6]设置为1来进行重置。

4.36.4 3DS操作

ECS功能支持3DS堆叠,其中芯片ID和命令位MR14 OP[3:0](分别为CID3:0)将ECS命令引导到堆叠内部的适当模式寄存器MR14-MR20。对于发往MR14或MR15的MRW命令,将忽略CID[3:0]位,导致3DS堆叠中所有芯片的相同透明设置。对于发往MR14-MR20的MRR命令,CID[3:0]位必须设置,以从3DS堆叠中的目标芯片读取数据。CID[3:0]位还将在手动ECS MPC命令中使用。对于单芯片封装,CID[3:0]位应全部设置为'0'。

模式寄存器的配置和模式寄存器数据的读出需要根据DRAM的寻址模式进行。不支持将手动ECS MPC命令广播给堆叠中的所有芯片。手动ECS MPC命令到命令间距需要等待tECSc,即使是发往堆叠中的不同芯片。在手动ECS操作的tECSc期间,只允许使用ODT NT命令。

本文详细介绍了DDR5内存的ECC错误检查和清除(ECS)模式,包括透明度实现、ECS模式设置、操作步骤、计数器管理、3DS堆叠支持等内容,强调了定期错误清除的必要性和操作注意事项。

本文详细介绍了DDR5内存的ECC错误检查和清除(ECS)模式,包括透明度实现、ECS模式设置、操作步骤、计数器管理、3DS堆叠支持等内容,强调了定期错误清除的必要性和操作注意事项。

3122

3122

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?