目录

源同步FPGA输入时序分析的模型

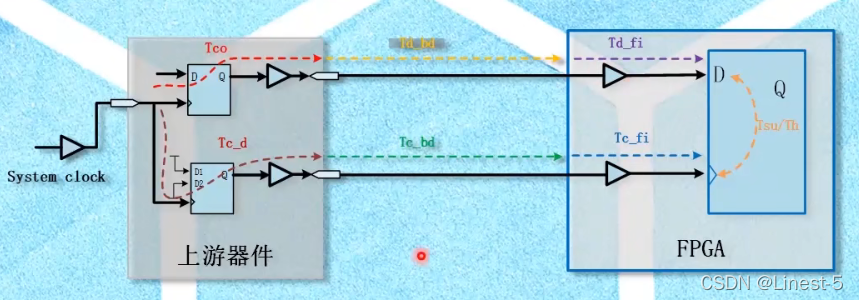

以下为源同步FPGA输入时序分析的模型的示意图,在之前的文章中介绍过,在此介绍一下各个时钟延时的含义。

Tco:到上游器件接口的数据延迟,这个延迟其实包括时钟源到寄存器D端的延迟、寄存器内部的延时Tco、Q端到输出接口的延迟,在这里统称为Tco。

Td_bd:数据延迟路径,板级布线的延迟(PCB)

Td_fi:FPGA内部到寄存器D端延迟,这部分的延时FPGA的综合工具类似Vivado是知道这部分的延迟情况是多少的。

Tc_d:到上游器件接口的时钟延迟。

Tc_bd:时钟路径延迟(PCB)

Tc_fi:FPGA内部到寄存器Clk端延迟。

input delay约束

在内部之间的约束(比如Td_fi、Tco、Tc_fi,建立时间门限、保持时间门限),时序分析工具是知道的,但是外部的这些延时量(比如Td_bd、Tc_d、Tc_bd等),时序分析工具是不知道的,因此就需要给它添加约束,就叫做input delay约束。

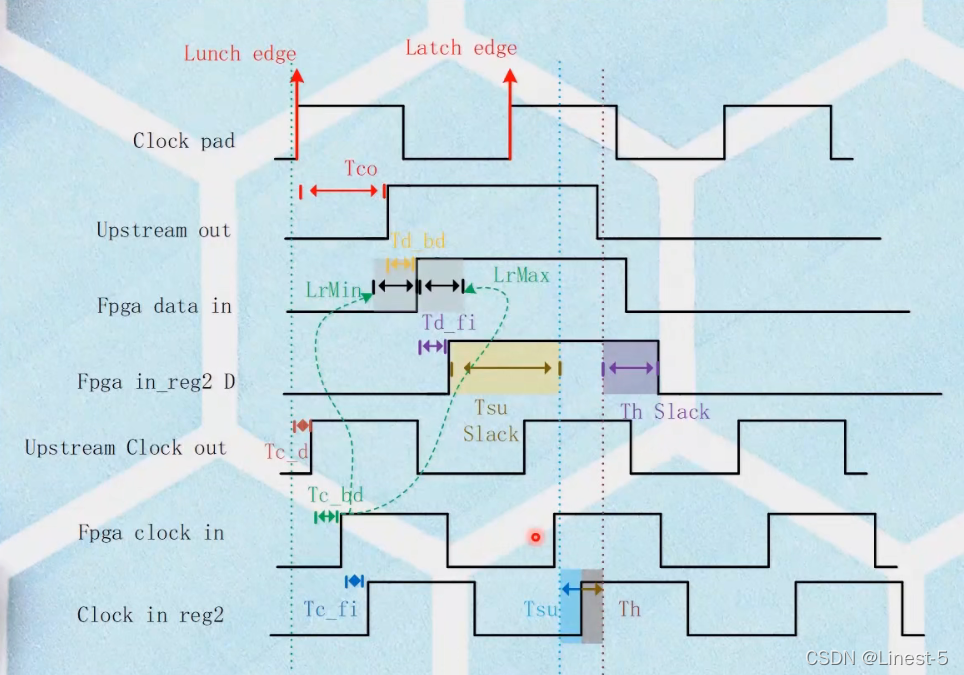

上图中的LrMin和LrMax表示由于在多条PCB布线时,有些线长有些短,这样就会导致延时的大小问题。

如果线长,延时就大,数据就会向右移,导致FPGA in_reg2 D的数据也会往右移,相应的建立时间余量就会被压缩;

相反的,如果线短,延时就小,数据就会向左移,导致FPGA in_reg2 D的数据也会往左移,相应的保持时间余量就会被压缩。

极限input delay

这里涉及到一个“极限input delay”(系统模型)的概念,它指的是当setup slack(建立时间余量)为0时,

极限input delay = Tcyc + Tc_d + Tc_bd + Tc_fi - Tsu

input delay(FPGA为中心) = 数据到达时间(FPGA引脚 )- 时钟到达时间(FPGA引脚)

input delay = Tco + Td_bd - Tc_d - Tc_bd

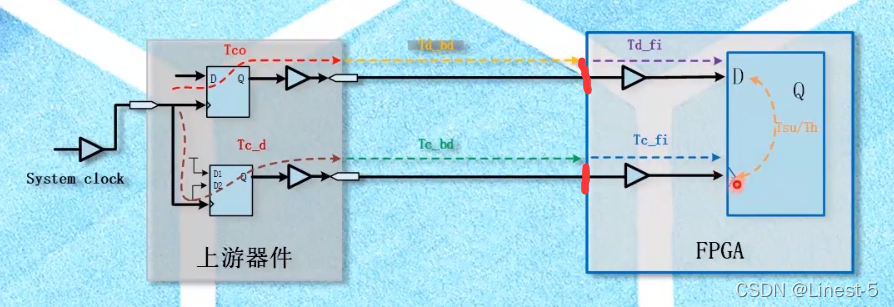

也就是说只看到FPGA一侧的比较,并没有到FPGA内部的寄存器,如下图,只到划红线的部分的比较。

前面说到

input delay = Tco + Td_bd - Tc_d - Tc_bd,这个input delay是存在最大最小值的

input delay MAX = Tco_max + Td_bd_max - Tc_d - Tc_bd

input delay MIN = Tco_min + Td_bd_min - Tc_d - Tc_bd

前面说了如果input delay越大就会压缩建立时间余量,而input delay越小就会压缩保持时间余量

如果取一个极端的情况:

在input delay MAX 的情况下能够满足建立时间的要求;

在input delay MIN 的情况下能够满足保持时间的要求;

那么在其他任何情况下,就都能满足建立时间和保持时间的共同要求了。

往期系列博客

【Xilinx Vivado时序分析/约束系列1】FPGA开发时序分析/约束-寄存器间时序分析

【Xilinx Vivado时序分析/约束系列2】FPGA开发时序分析/约束-建立时间

【Xilinx Vivado时序分析/约束系列3】FPGA开发时序分析/约束-保持时间

【Xilinx Vivado时序分析/约束系列4】FPGA开发时序分析/约束-实验工程上手实操

【Xilinx Vivado时序分析/约束系列5】FPGA开发时序分析/约束-IO时序分析

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?