引言

DFT是ASIC芯片设计流程中不可或缺的环节。其主要目的是在芯片前端设计验证完成后插入一些诸如寄存器链等可供测试的逻辑,算是IC后端设计的范畴,属于结构测试而非功能测试。主要是在ASIC芯片流片完成后,通过这些已插入的逻辑,检测流片得到的芯片的制造质量。检测一些固定故障等。

学习参考

- 数字系统测试和可测试性设计。【美】赛纳拉伯丁 - 纳瓦比 著。原本和译本。

- 修真院讲解视频。

- E课网 DFT 课程。

- 华中科技大学IC设计中心 陈新武 讲稿《集成电路测试方法研究》。

- Design-for-Test: Scan and ATPG Training Student Workbook ,Copyright Mentor Graphics。

故障建模

对芯片制造过程中可能出现的制造缺陷进行建模,可以帮助分析具体故障以及产生测试向量。

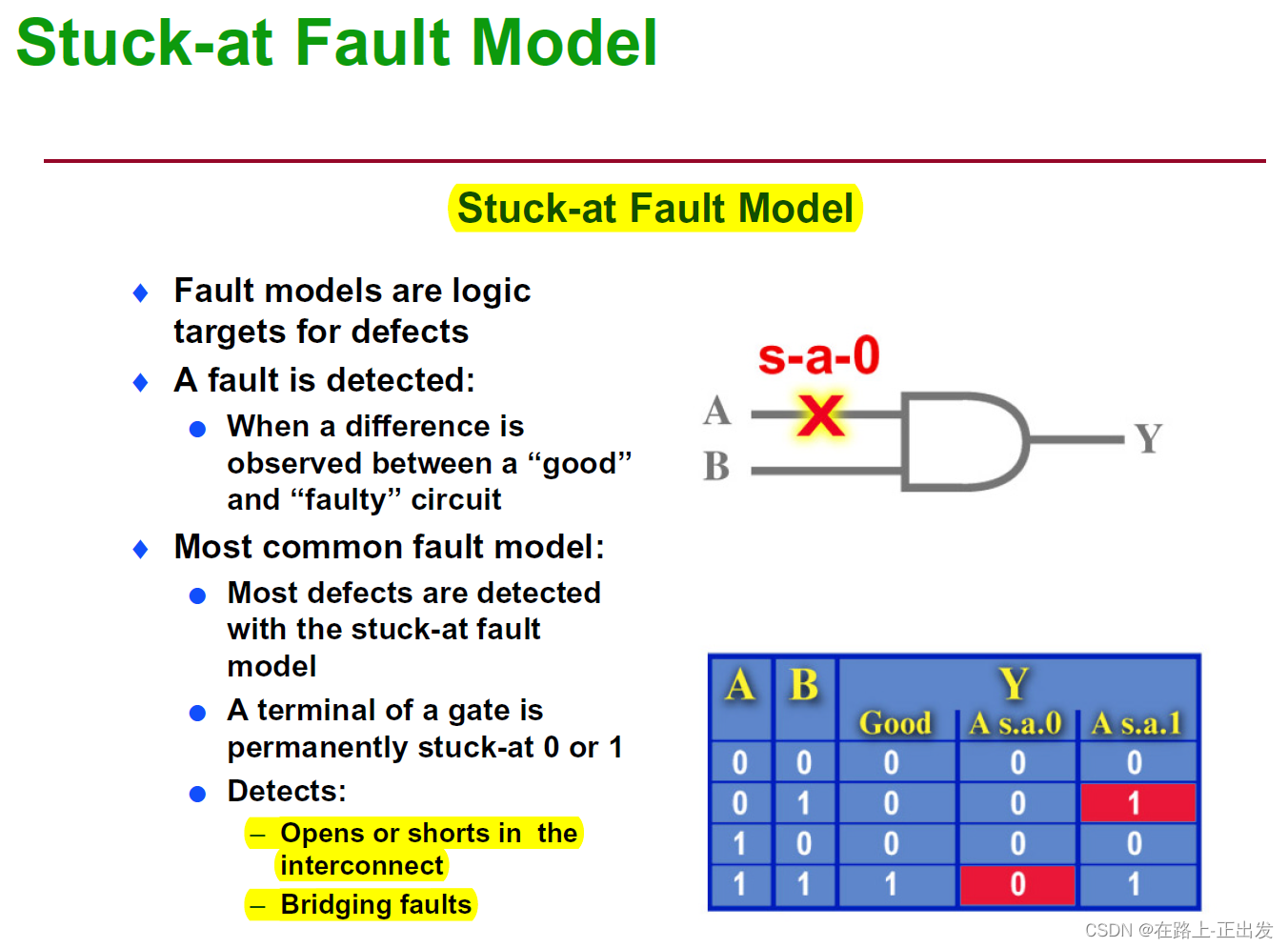

Stuck-at 故障模型

芯片制造过程中由于工艺或者环境控制不佳,导致某些芯片内的布线出现stuck-at问题,即该布线的电平被始终拉高或者拉低。

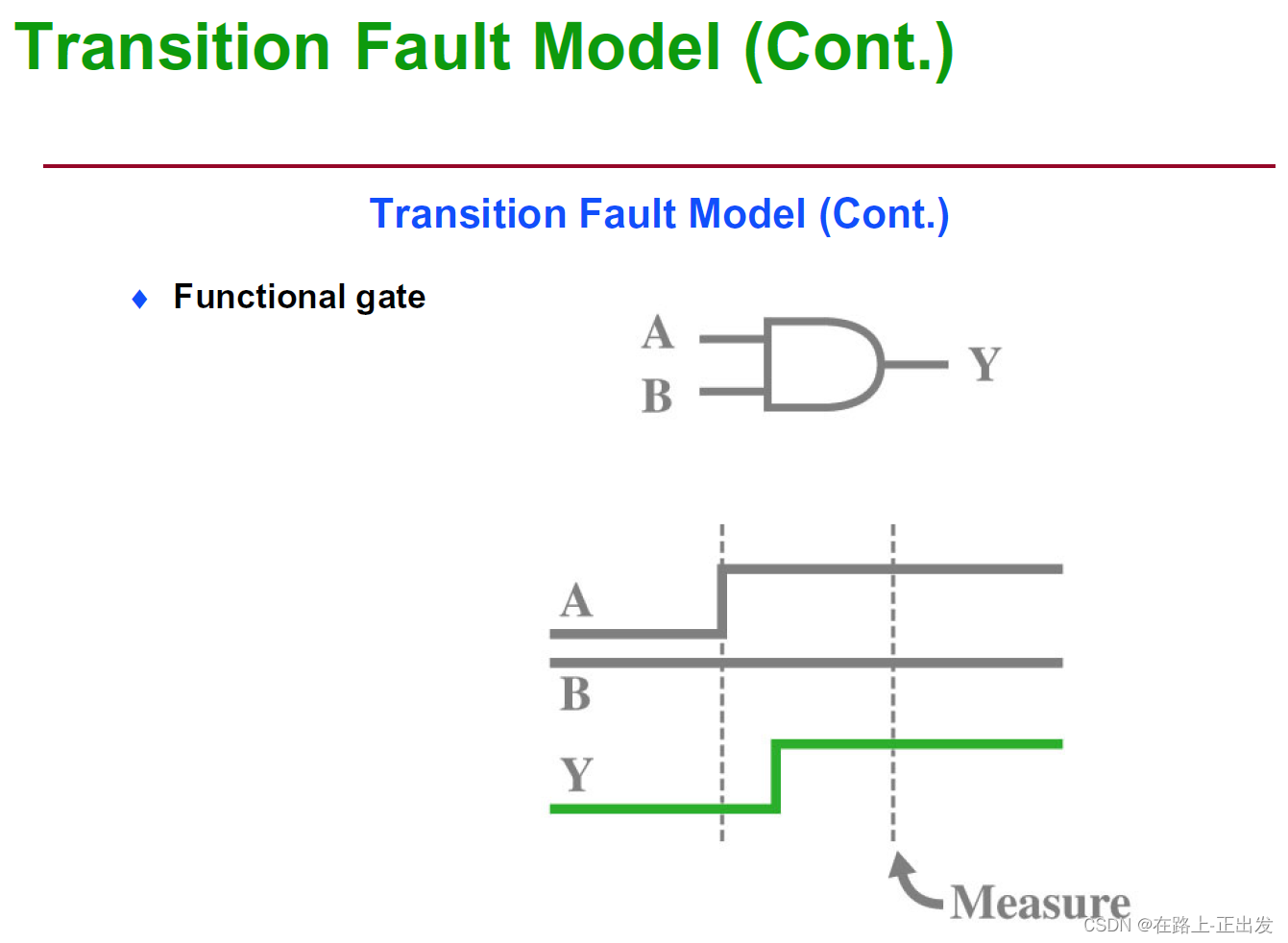

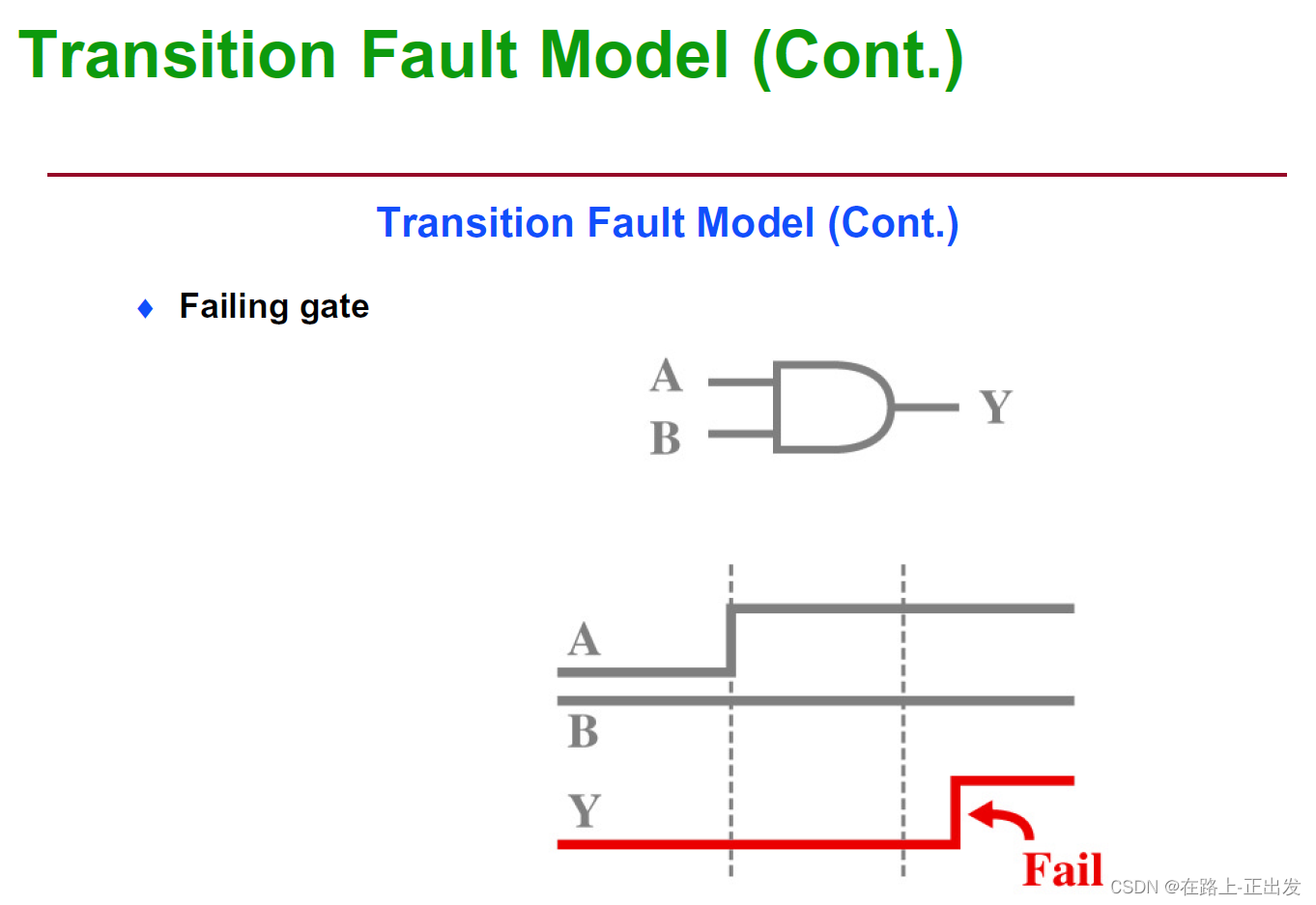

翻转(transition)故障模型

电平转换时间变长,即时钟或者数据的边沿跳变时间边长,速率变慢。

对比一下:

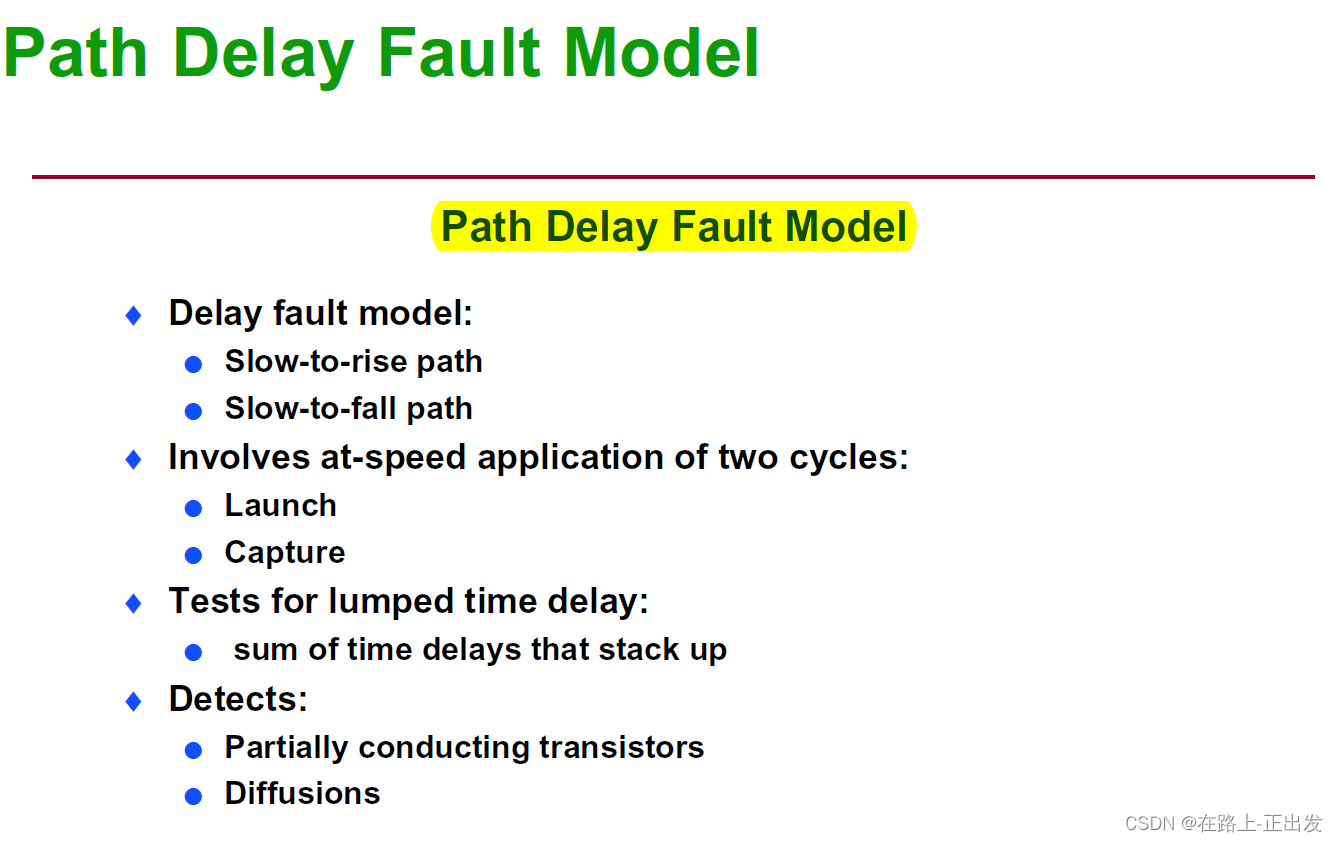

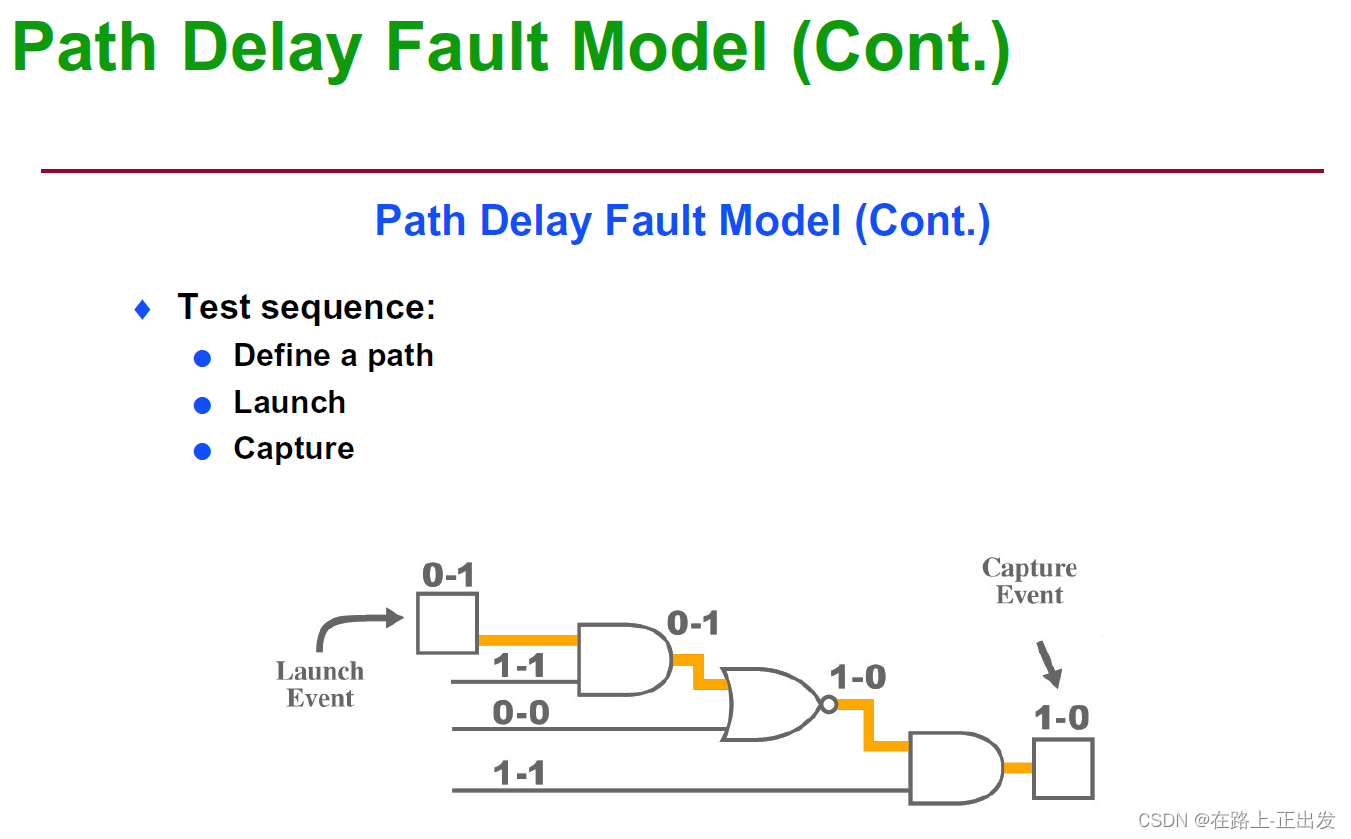

路径延时故障模型

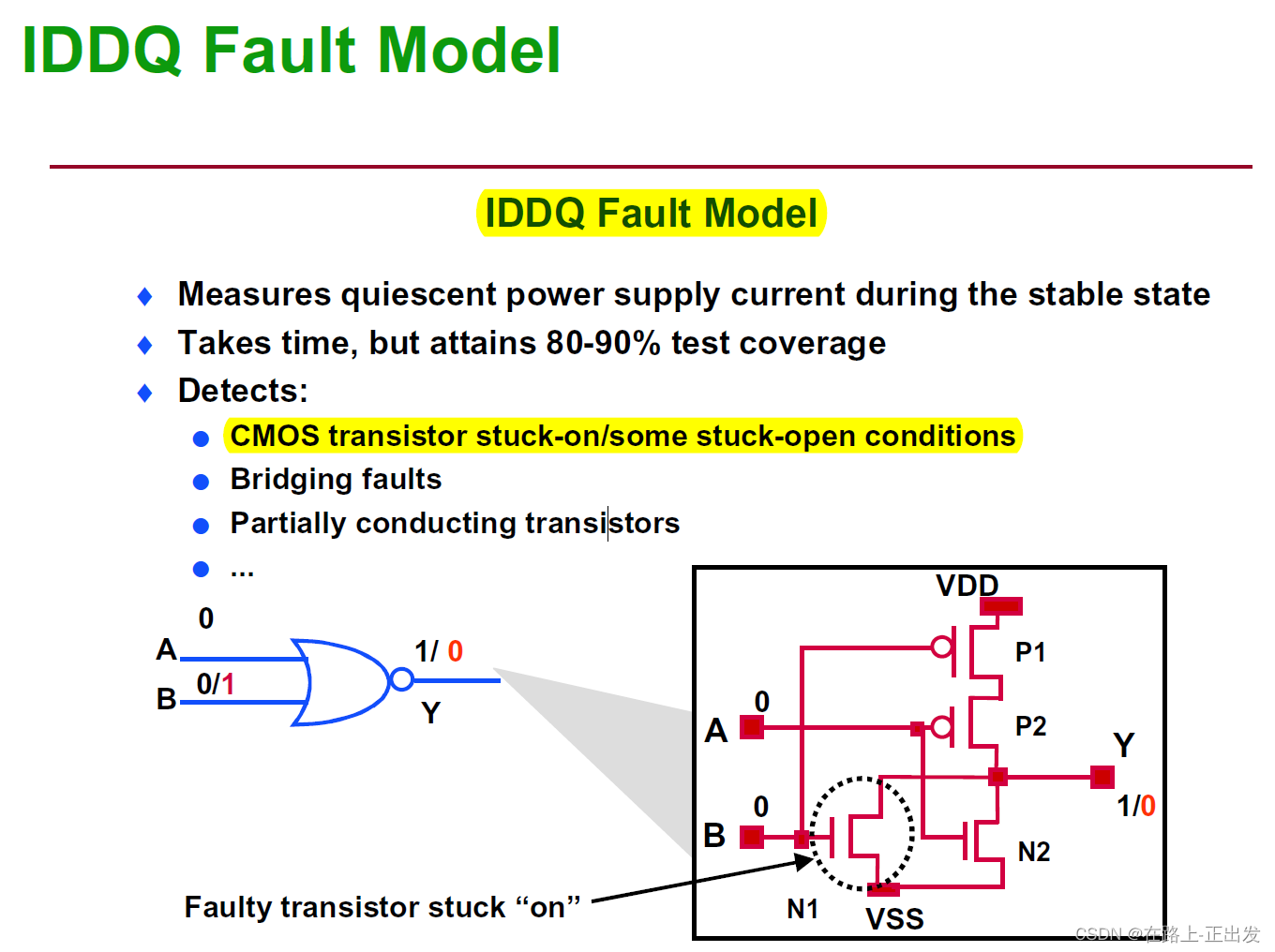

静态电流测试

不了解的点击这里:IDDQ简介

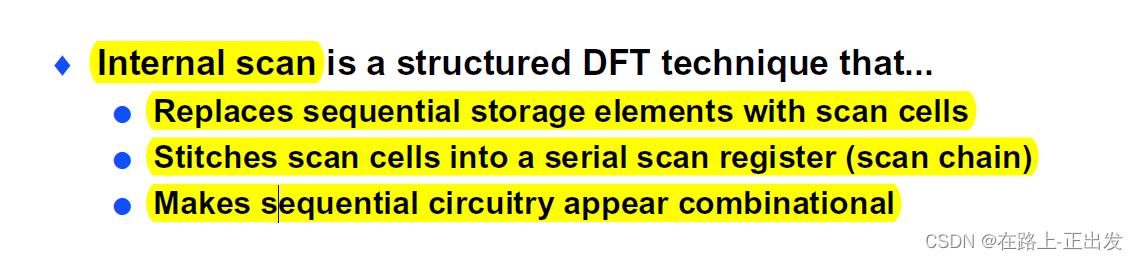

扫描 (Scan) 技术

基本说明

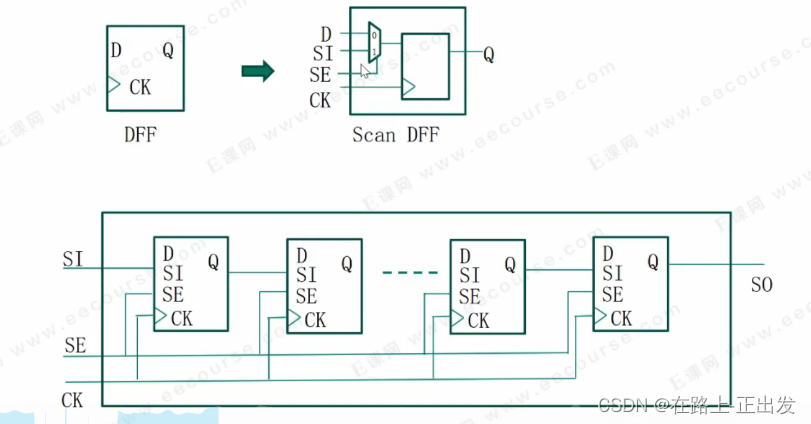

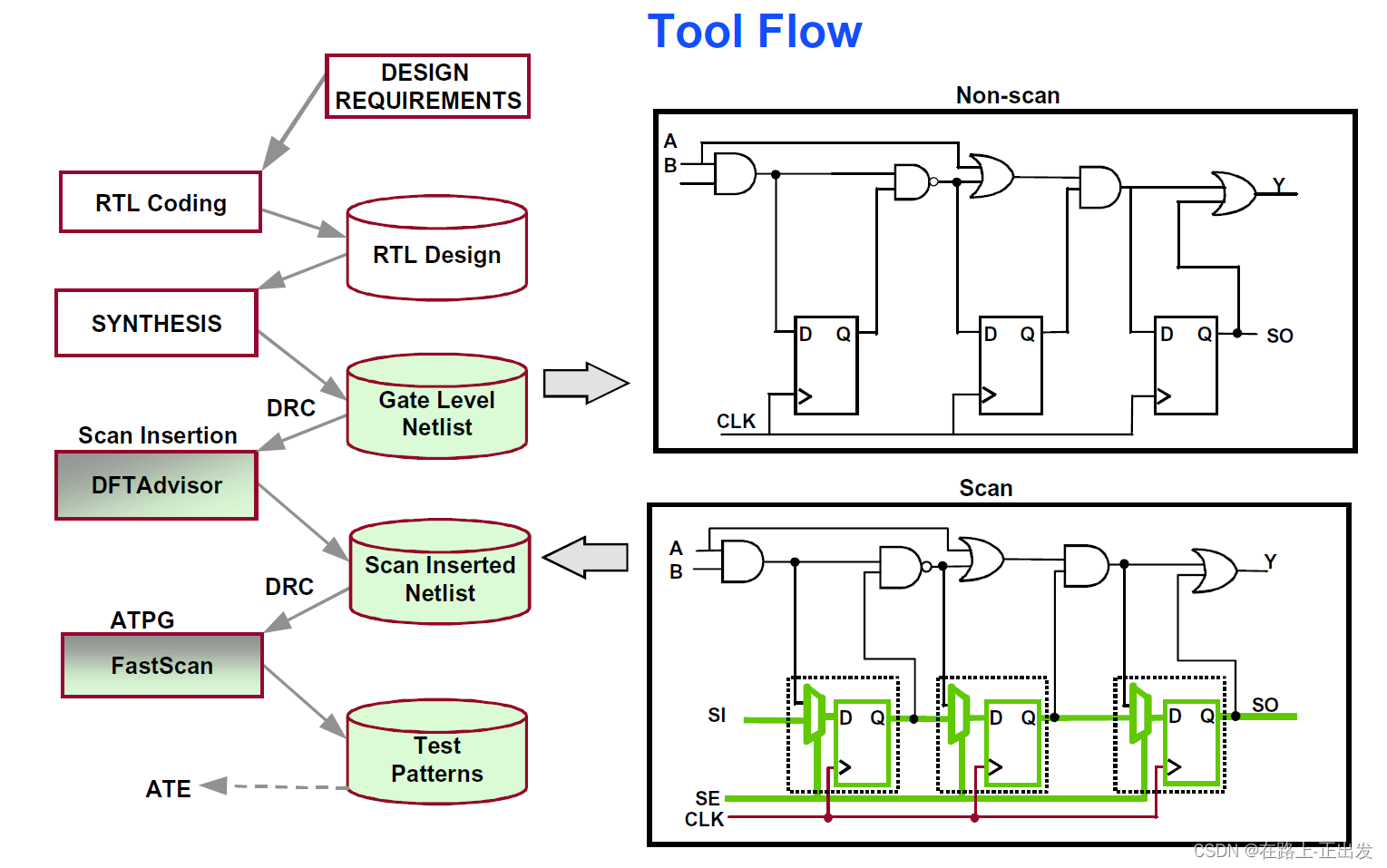

如下图所示,首先是触发器替换,将普通的触发器,替换为扫描触发器。然后是将各个扫描触发器串联起来。

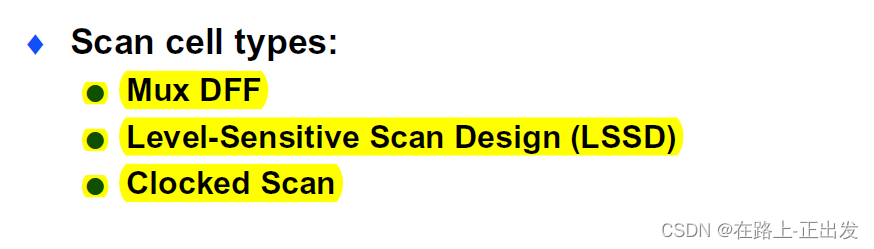

Scan Cell Type

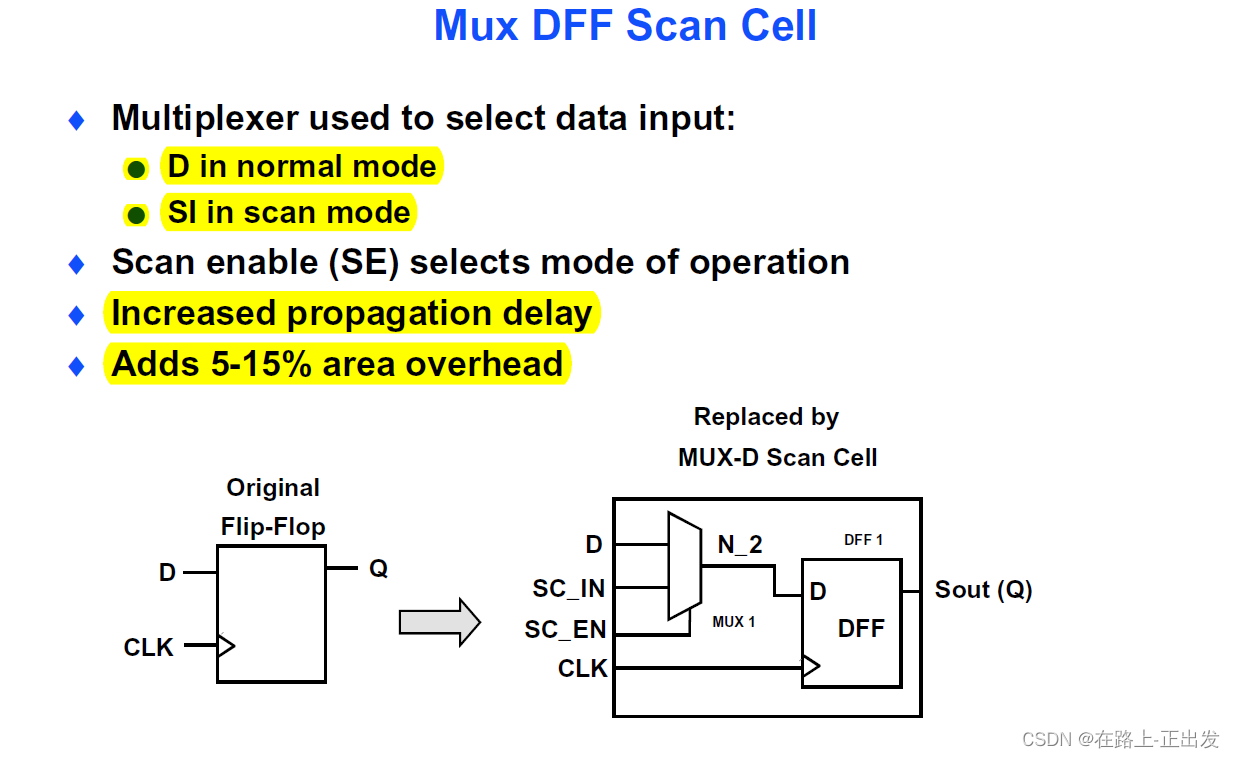

采用多路选择器而增加的延迟表现在功能路径中,有较少的面积增加。一个带多路选择器的D触发器通常将一个标准D触发器的面积增加15%到30%;增加的I/O端口最少的可以只有一个Scan_En。在实际设计中,可能并不需要增加一个另外的I/O端口用于Scan_in或者Scan_out,因为可以在设计中将这些引脚和功能引脚复用。

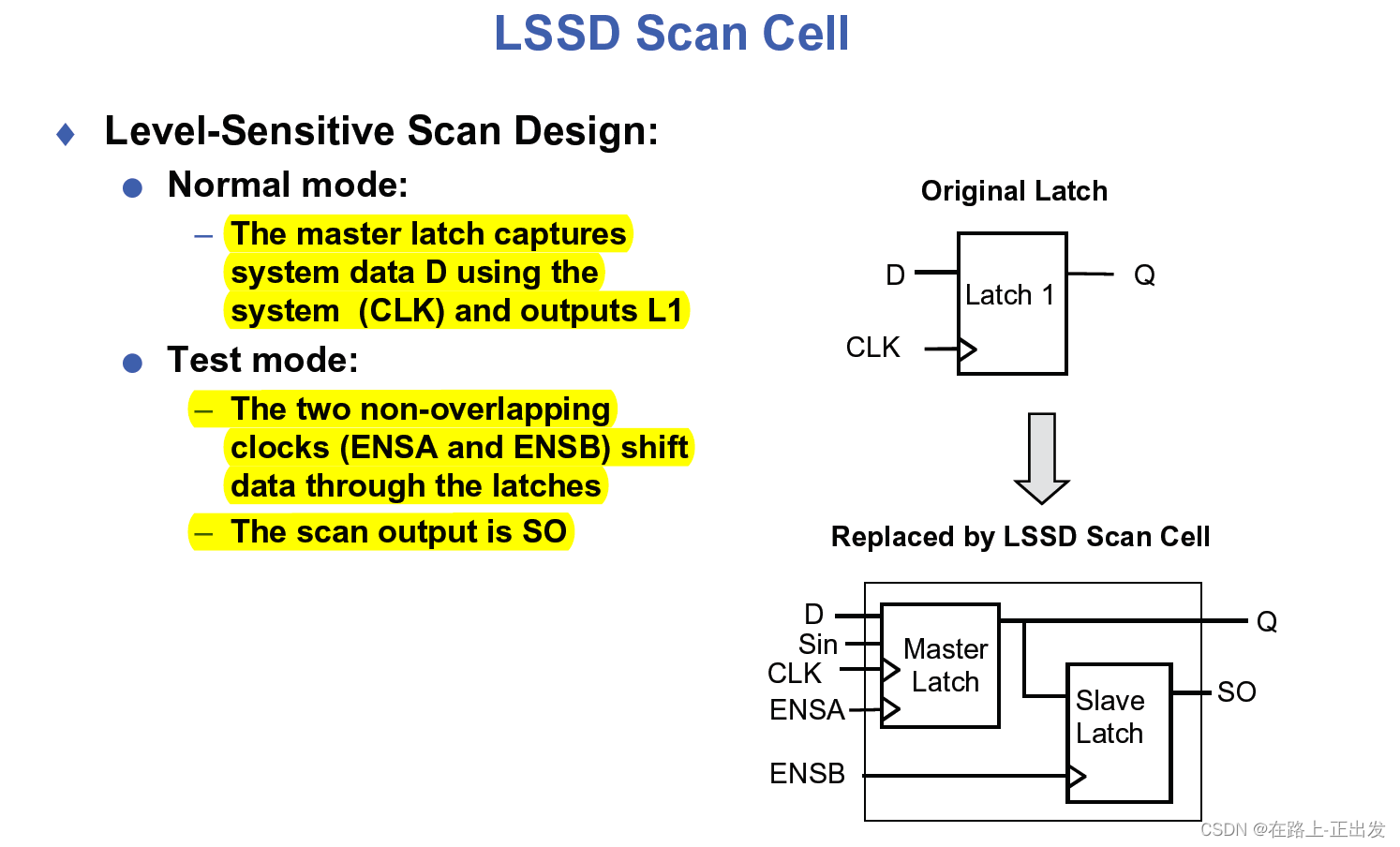

单锁存电平敏感扫描单元的逻辑结构如图所示。上图为通常意义下的D触发器,下图为它相应的可扫描单元。增加了一个数据输入端、两个时钟输入端: Test_Scan_Clock_a 和Test_Scan_Clock_b。增加的两个时钟是电平触发的。在测试模式下,Test_Scan_Clock_a和Test_Scan_Clock_b连接到所有的同类扫描单元,分别在不同的时刻将扫描数据逐位移动。Scan_in引脚的数据来自上一个扫描单元。

单锁存器LSSD的特征是:

a) 对电路性能的影响可以忽略;

b) 较高的面积代价。用一个LSSD单元替换一个简单的锁存器将会增加100%或者更多时序逻辑的面积。增加的主测试时钟和从测试时钟也增加了布线的面积(与多路选择器型的触发器扫描类型相比);

c) 支持带有异步复位和清零端的锁存器;

d) 因为增加了专用的测试时钟,所以适合用于部分扫描设计。

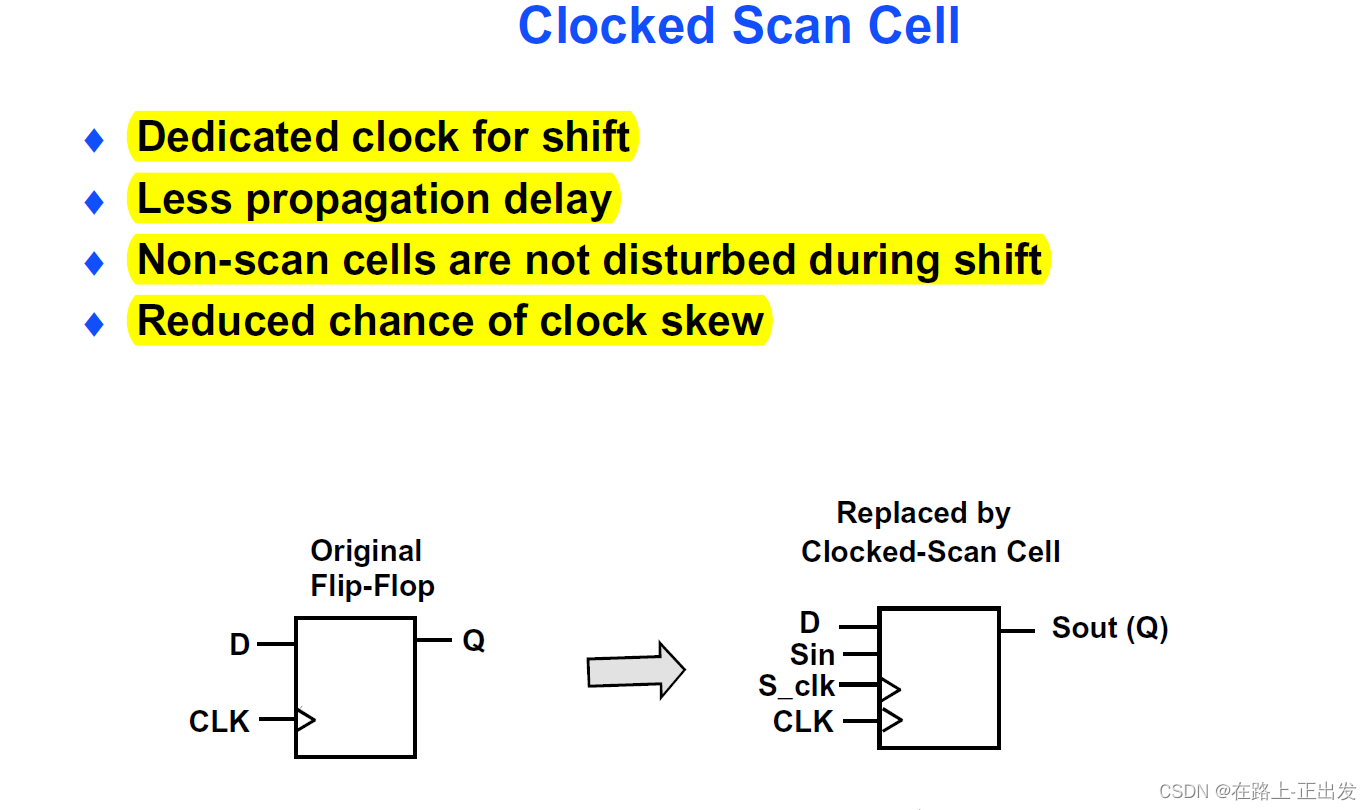

专用时钟控制的扫描方法是使用一个专用的、边沿触发的测试时钟来提供串行移位驱动。在功能模式下,系统时钟是活动的,系统数据被时钟打入单元电路。在测试移位过程中,测试时钟是活动的,扫描数据被打入该电路单元。电路符号如图4-2所示。图a为标准的D触发器,图b为专用时钟控制的可扫描单元。在这种结构中,相当于有两个D输入端,两个时钟输入端。在这种方式下,需要增加的测试引脚有:扫描输入、测试时钟、扫描输出(可以和输出功能引脚共用)。

专用时钟控制扫描方式的特征是:

对电路性能影响可以忽略;面积的增加可以接受:一个专用时钟控制的扫描单元一般比普通的D触发器的面积增加15%--30%;支持这种扫描方式的工艺库具有触发器和锁存器两种等效单元;很适用于部分扫描设计:专用的测试时钟提供了一种机制,在扫描移位的过程中,可以很容易地保持非扫描单元的状态;支持带有异步置位和复位端的锁存器;典型的应用是具有边沿触发的设计风格。

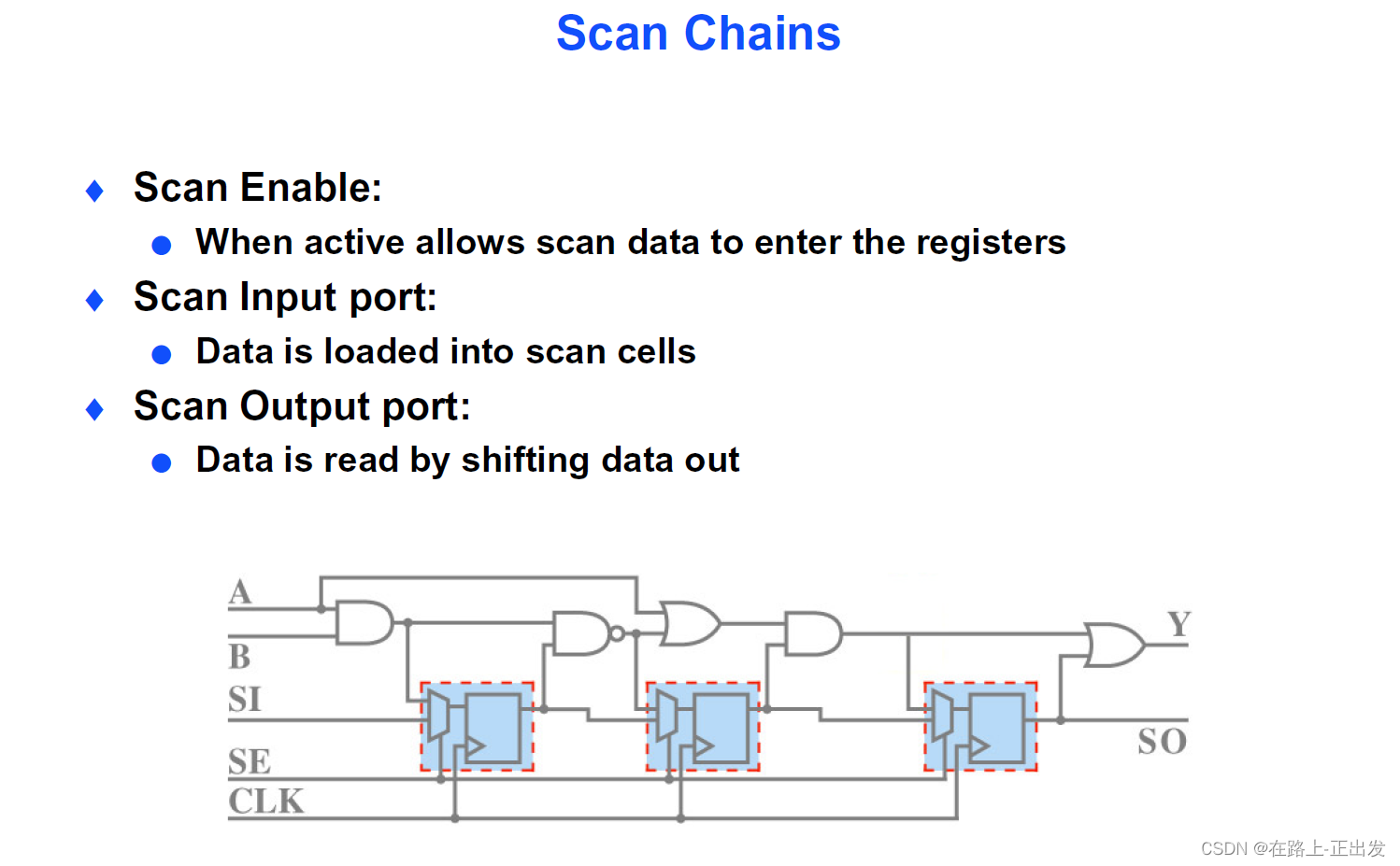

Scan Chains

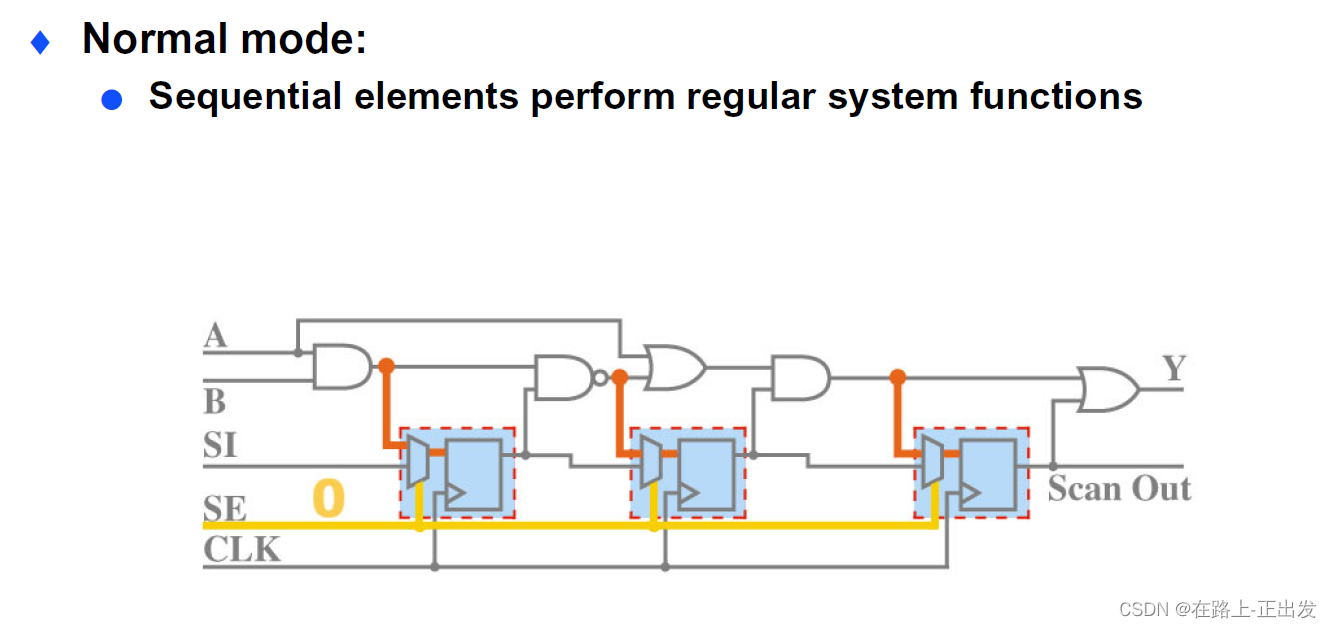

正常模式

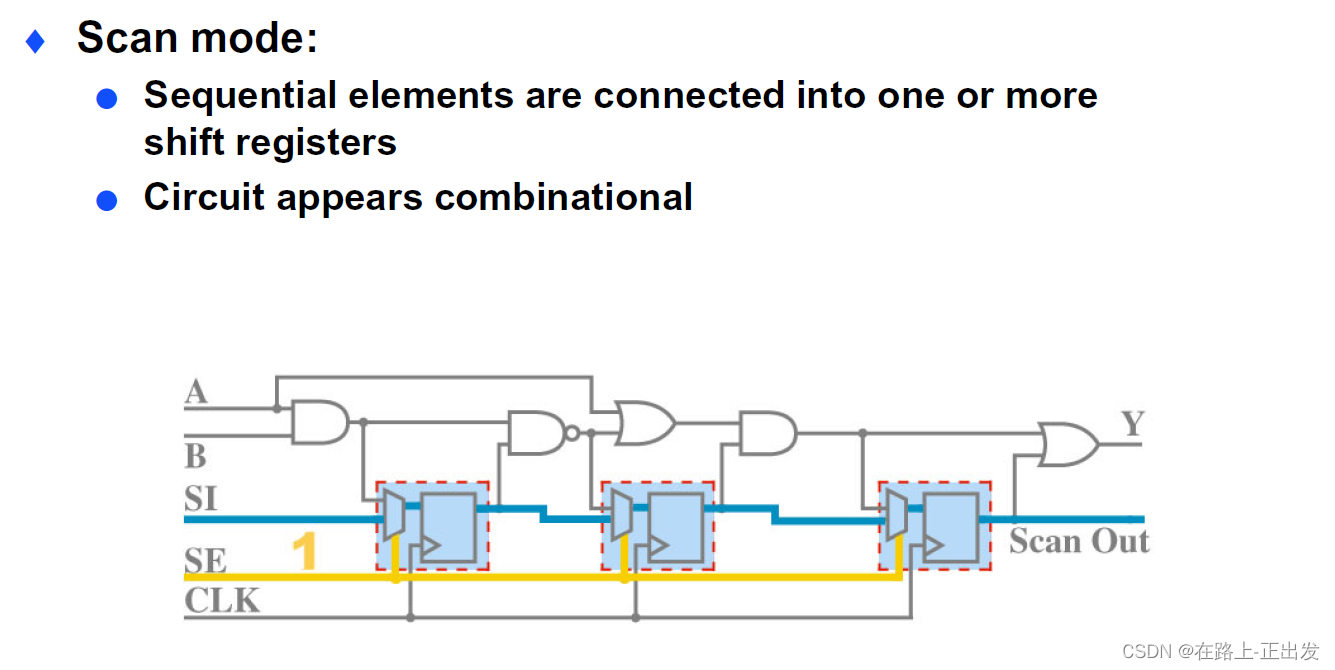

扫描模式

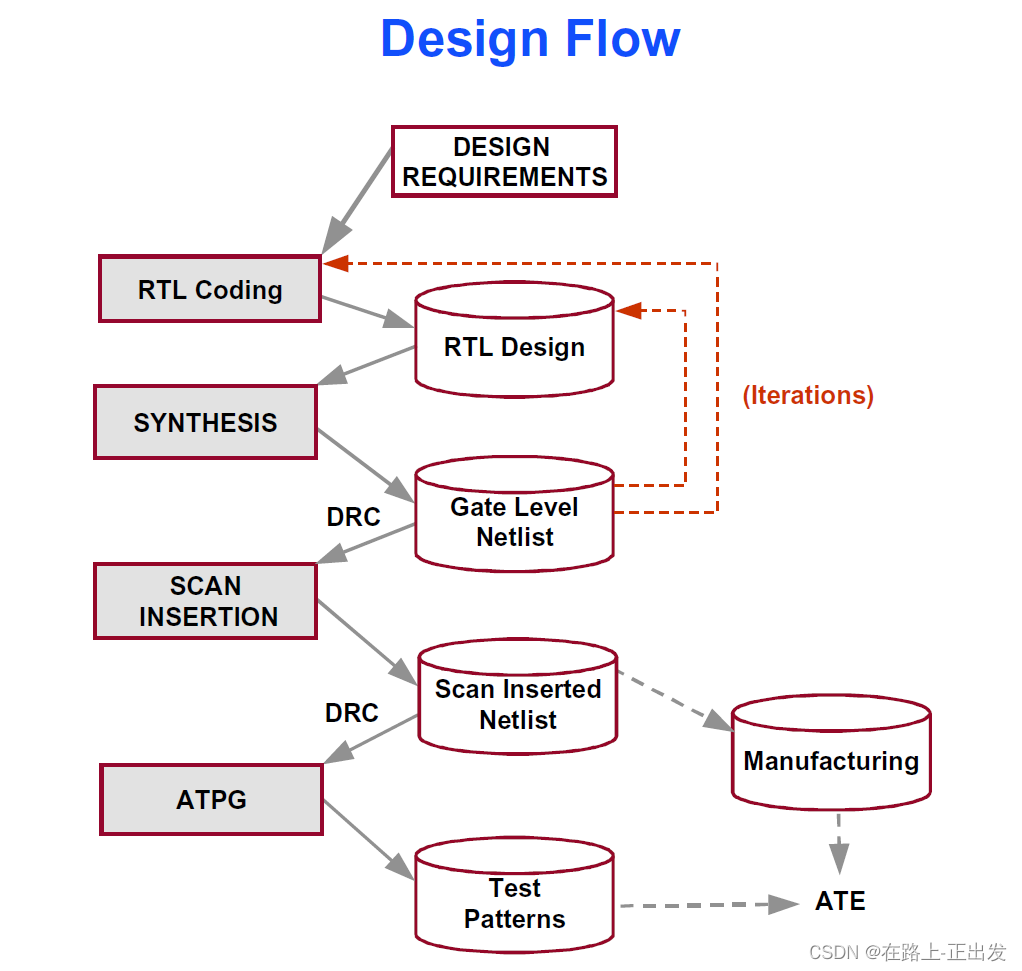

设计流程

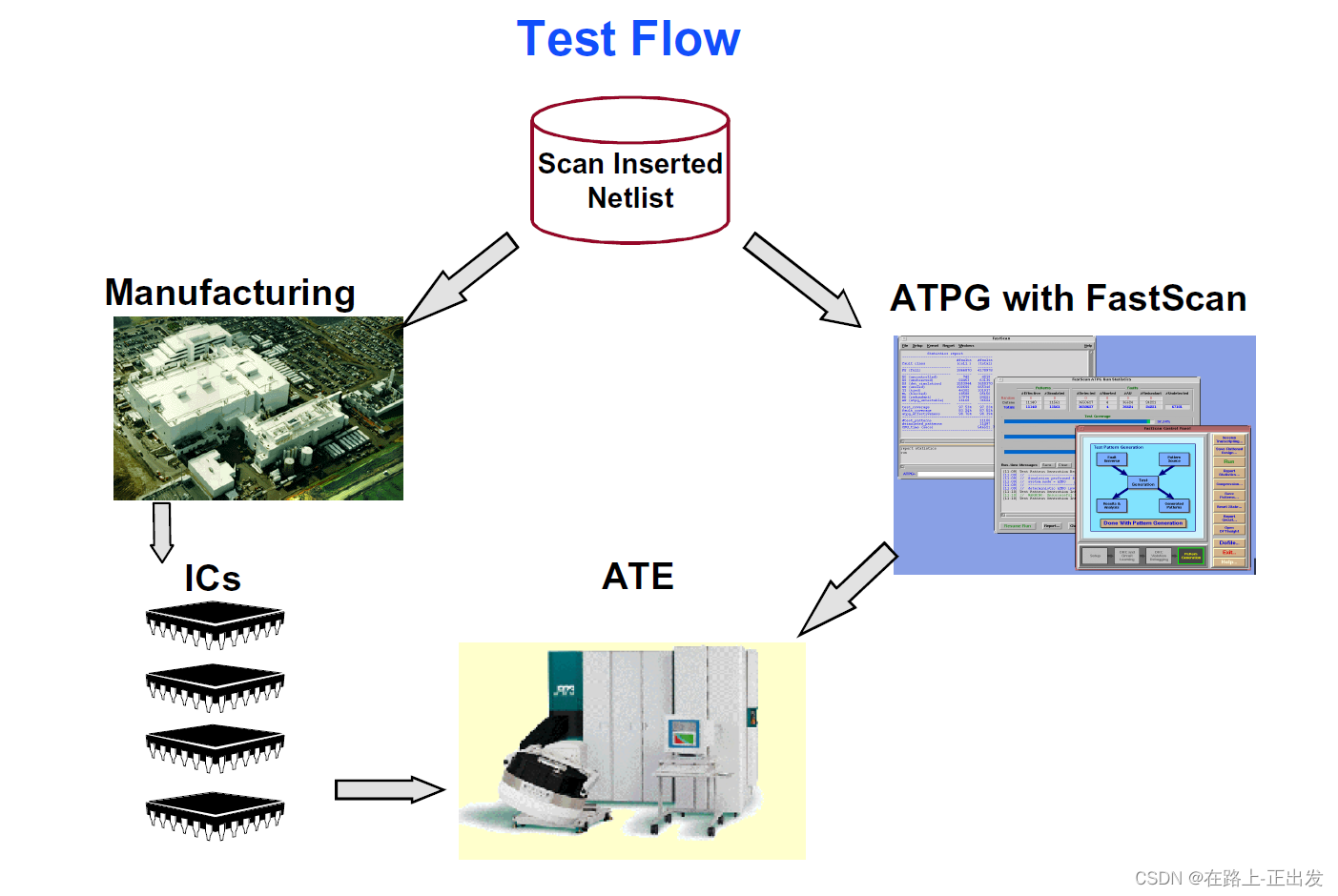

测试流程

工具流程

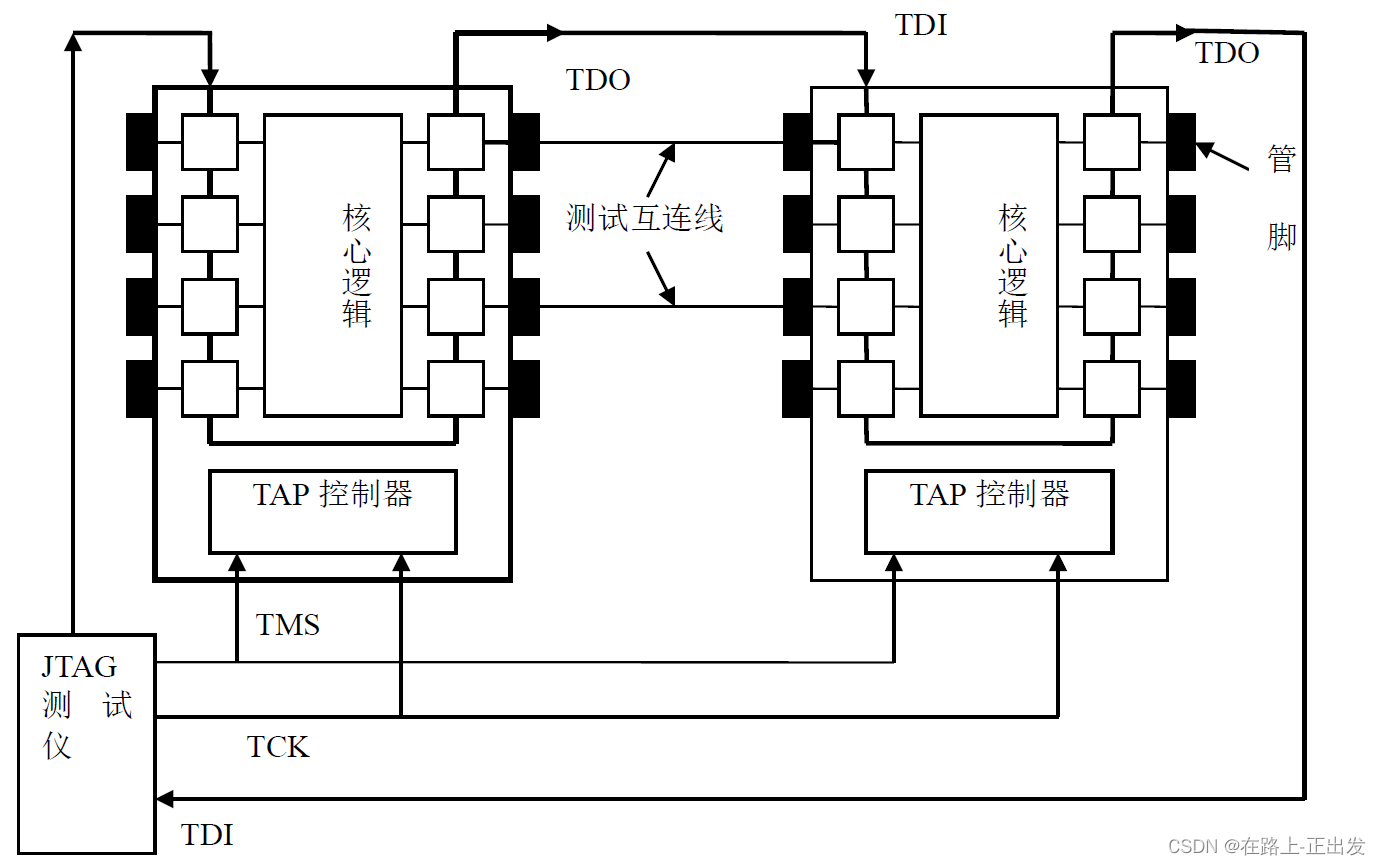

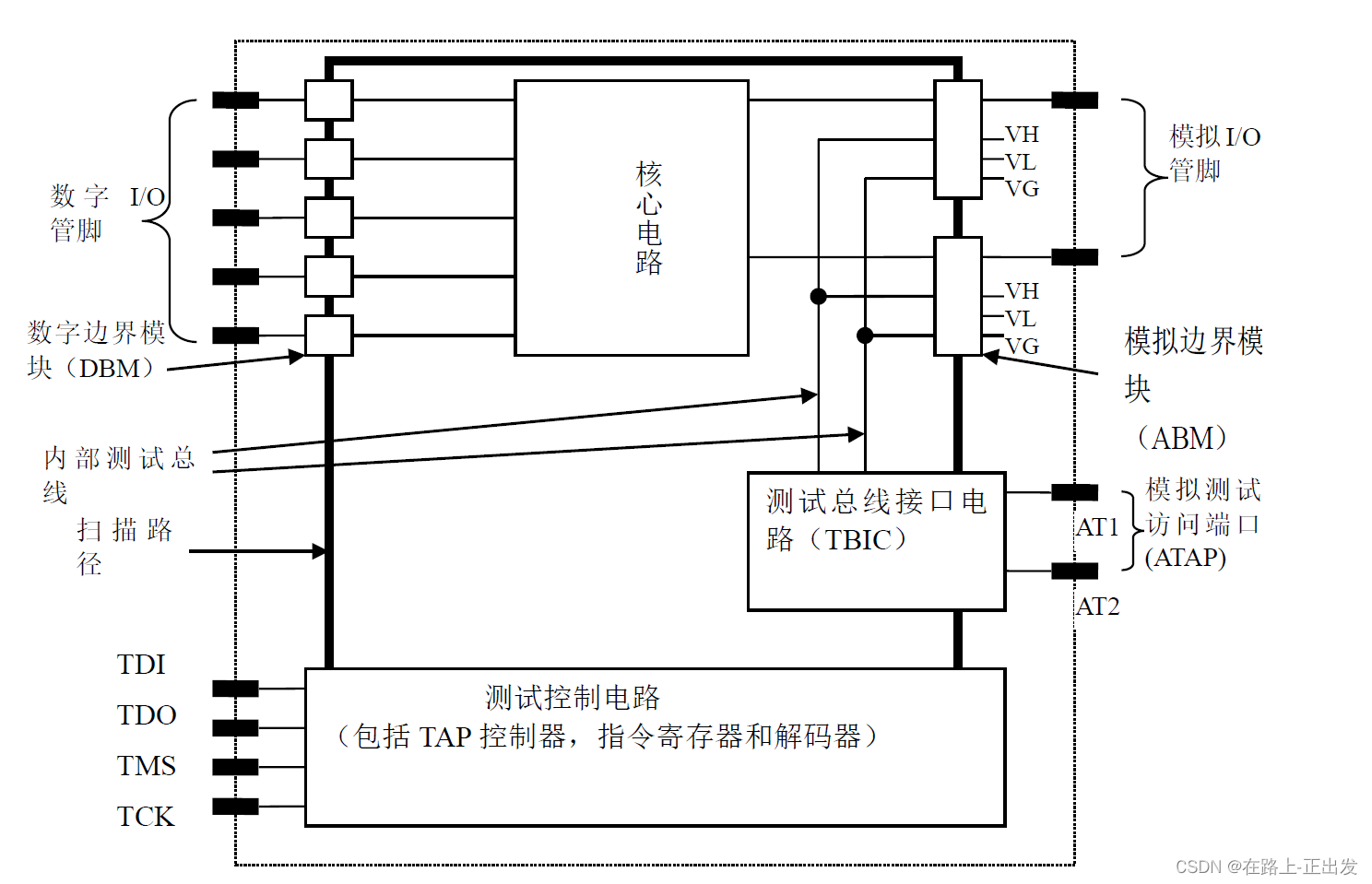

边界扫描

移位寄存器单元插入到IC的核心逻辑与I/O管脚之间,以提供通过所有IC的一条串行测试数据通路。因为移位寄存器单元位于IC的边界处,所以这些单元被称为边界扫描单元(BSC,Boundary Scan Cell),由它们构成的移位寄存器称为边界扫描寄存器。串行测试数据的输入端被称为测试数据输入端(TDI),相应的输出端被称为测试数据输出端(TDO)。为了完成测试功能,相互连接的边界扫描单元必须具有数据移位、数据更新、数据捕获等功能,这些功能是由测试控制逻辑来控制的。测试控制逻辑由两条信号线驱动:测试方式选择(TMS)和测试时钟(TCK)。所以,整个边界扫描测试要求IC中至少有四个可利用的测试管脚,或将它们附加到其他的功能管脚上。

边界扫描测试技术的工作原理就是:JTAG测试仪利用一个四线测试接口,将测试数据以串行方式由TDI打入到边界扫描寄存器中,通过TMS发送测试控制命令,经TAP控制器控制边界扫描单元完成测试数据的加载和响应数据的捕获。最后,测试响应数据以串行扫描方式由TDO送出到JTAG测试仪,在那里,将捕获到的响应数据与期望的响应进行比较。四个管脚TMS、TCK、TDI和TDO被称为测试访问端口(TAP, Test Access Port),全部测试控制逻辑被称为TAP控制器。

内建自测 BIST

BIST主要完成测试序列生成和输出响应分析两个任务。通过分析被测电路的响应输出,判断被测电路是否存在故障。因此,对数字电路进行BIST测试,需要增加三个硬件部分:测试序列生成器、输出响应分析器和测试控制部分。

确定性测试方法是一种针对特定的电路故障进行测试的方法,虽然可以得到很高的故障覆盖率,但硬件开销大,仅在测试码个数较少的时候采用。

伪穷举测试的方法是把所有可能输入都加以计算的测试方法。它的最大特点是故障覆盖率可以达到100%,但其计算量与输入端子呈幂次方关系,因此计算量很大。如果将电路分为多个原始输入变量互相独立的块,则测试数将大大减少。伪穷举法就是这样一种压缩测试向量的方法。伪穷举法也具有很高的故障覆盖率,但伪穷举法对电路进行划分比较困难,有相当的局限性。而且由于加入了附加硬件,可能对电路性能产生负面效应。

伪随机测试是一种广泛使用的测试方法,该方法可以对被测试电路产生大量的测试代码,而且硬件电路开销较小,同时具有较高的故障覆盖率。LFSR(Linear Feedback Shift Register,线性反馈移位寄存器)就是这样一种测试代码生成电路。

实现输出响应分析的方法有ROM比较逻辑法、多输入特征寄存器法和跳变计数器法等。ROM比较逻辑法是将正确的响应存储在芯片内的ROM中,在测试的时候,将其与测试响应进行比较,但这种方法会因为占用太多的芯片面积而毫无实用价值。多输入特征寄存器方法是将被测试电路中各节点的响应序列进行处理,得到与测试响应序列等长的特征字(Signature),然后与无故障电路节点的响应序列特征值进行比较,如果两者相同,则说明电路正常,否则表明被测试电路有故障存在。跳变计数器法是通过比较输出响应的跳变总数,来判断被测试电路是否正常工作,因此需要存储和比较跳变次数,从而使得所需要的存储空间与测试时间都得到大幅度的降低。但是后面两种方法是以牺牲故障覆盖率为代价的。

2667

2667

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?