时钟 区域

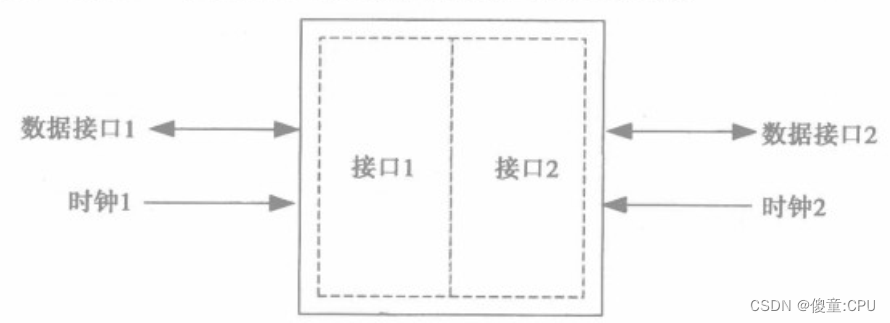

本文所指的时钟区域时一段逻辑,其中全部的同步元件(触发器、同步RAM块、流水线乘法器)使用同一网线定时。如果全部的触发器都使用一个全局网线定时,主时钟输入到FPGA,则有一个单时钟区域。如果有两个时钟输入到这个设计中,比如说一个为“接口1”,一个为“接口2”。

门控时钟、分频时钟和事件驱动的触发器全部归入时钟区域的类别。

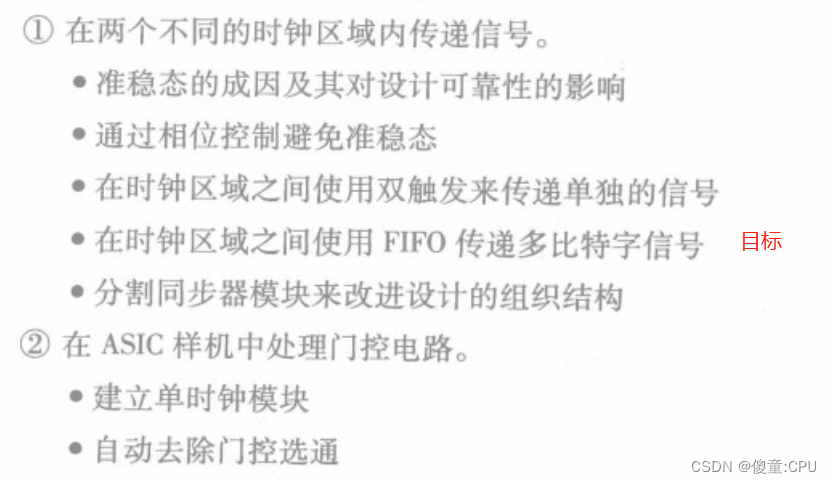

1、跨越时钟区域

在处理多时钟区域时首先需要强调的问题是在区域之间传递信号的问题。有许多原因时钟区域跨越可能是一个主要问题:

- 故障不总是可再现的。如果有两个异步时钟区域,故障通常与时钟沿之间的相对时序有关系。时钟通常又是来自与器件的实际功能没有任何相关的外部源。

- 问题可能从工艺到工艺变化。常常发现对建立和保持约束较小的高速工艺统计上比低速工艺更少出问题。同时,一些因素:像同步器件的实现。输出缓冲的方式,也将对故障概率产生重大影响。

- 一般地,EDA工具都不检测和标注这些问题。静态时序分析工具是基于单个时钟区域分析时序,并且如果以一种特殊的方式来专门做着方面的工作,也只是执行时钟间的分析。

- 通常情况下,如果不能判断出来,跨时钟区域的故障很难检测和诊断,任何实现开始之前,正确定义和处理全部之间的接口是非常重要的。

订阅专栏 解锁全文

订阅专栏 解锁全文

8255

8255

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?