标题

Experimental demonstration, challenges, and prospects of the vertical SiC FinFET(ISPSD2022)

文章的研究内容

- 实验演示

研究团队首次成功制备了垂直、常关型高压SiC FinFET。该器件基于沟槽技术,鳍宽度( W fin W_{\text{fin}} Wfin)为144nm,实现了以下关键性能:

- 击穿电压达1kV

- 导通电阻( R on R_{\text{on}} Ron)低至0.7mΩcm²

- 阈值电压(

V

th

V_{\text{th}}

Vth)为2.2V

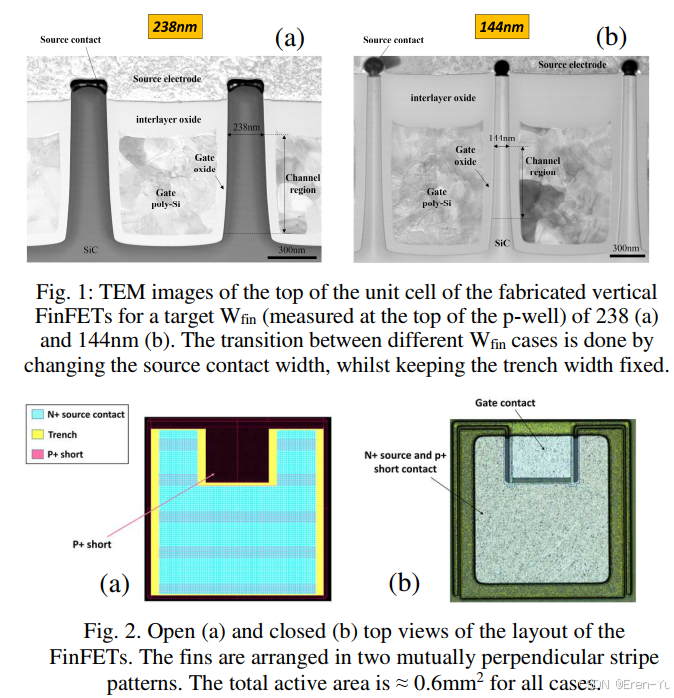

通过透射电子显微镜(TEM)图像验证了结构的精确性(图1-2),并通过TCAD模型仿真了器件电场分布(图3-4)。

-

FinFET效应分析

FinFET效应通过三重机制提升器件性能:- 减少耗尽电荷,增强反型层电荷密度;

- 减弱表面散射,使沟道远离MOS界面;

- 降低横向电场,提高载流子迁移率。

实验发现,当鳍宽度减至144nm时,体传导显著增加(图6),阈值电压降低,且跨导特性更陡峭(图5),验证了FinFET效应的存在。

-

TCAD建模与实验验证

开发了基于Synopsys Sentaurus的TCAD模型(图4),通过调整库仑散射参数与界面态密度( D it D_{\text{it}} Dit),模拟结果与实验数据在300K下基本吻合。然而,在阈值电压附近存在偏差,推测源于实际 D it D_{\text{it}} Dit分布与假设的差异(图5)。模型还揭示了144nm器件的固定电荷密度( N fs N_{\text{fs}} Nfs)较高( 2.35 × 1 0 12 cm − 2 2.35 \times 10^{12} \, \text{cm}^{-2} 2.35×1012cm−2),但阈值电压降低的主因仍为FinFET效应。

文章的研究方法

1. 器件制备与实验设计

- 目标结构:制备了不同鳍宽度(850nm、550nm、344nm、238nm、144nm)的垂直SiC FinFET,通过改变源极接触宽度调整鳍间距,同时保持沟槽宽度固定(图1)。

- 外延层设计:

- 击穿电压优化:外延层厚度8μm,掺杂浓度1.8×10¹⁶ cm⁻³(n型),并包含1.5μm厚的电流扩展层(掺杂10¹⁷ cm⁻³)和90μm厚的重掺杂衬底(10¹⁸ cm⁻³)。

- 栅极氧化:氧化层沿(1-100)晶面生长,锥角约3.5°,以优化界面特性。

- 结构验证:通过**透射电子显微镜(TEM)**对鳍结构进行成像(图1-2),确保工艺精度。

2. TCAD建模与仿真

- 模型构建:

- 使用Synopsys Sentaurus工具建立三维TCAD模型(图4),采用条纹近似法模拟真实器件的活性区域。

- 引入p型掺杂柱以模拟p+短接结构的横截面积,确保所有设计的一致性。

- 物理机制建模:

- 迁移率模型:结合库仑散射、表面声子散射和粗糙度散射,引用文献公式量化散射效应。

- 界面态密度(Dₕ):基于实验数据校准,假设Dₕ分布参考前期研究(如文献[5])。

- 参数校准:通过调整模型参数(如固定电荷密度 N fs N_{\text{fs}} Nfs),在300K下匹配实验I/V特性(图5),验证模型可靠性。

3. 实验验证与数据分析

- 电学特性测试:

- 击穿电压测试:在关态条件下( V gs = 0 V V_{\text{gs}}=0\text{V} Vgs=0V),验证器件击穿电压超过1kV(图3)。

- 导通特性分析:测量不同鳍宽度器件的转移特性曲线(图5a),提取阈值电压( V th V_{\text{th}} Vth)和跨导( g m g_m gm)变化规律。

- 载流子行为分析:

- 通过TCAD模拟载流子密度分布(图6a)和电流密度分布(图6b),揭示144nm鳍器件中体传导与界面传导的竞争机制。

- 结合电子准费米能级分布(图9),量化器件内部电阻分量(如沟道电阻 R ch R_{\text{ch}} Rch、衬底电阻 R sub R_{\text{sub}} Rsub等),解释导通电阻随鳍宽变化的非线性趋势(图7-8)。

4. 理论分析与优化策略

- FinFET效应机制:通过三维电场分布与载流子输运模型,提出三重作用机制(减少耗尽电荷、减弱表面散射、降低横向电场)提升迁移率。

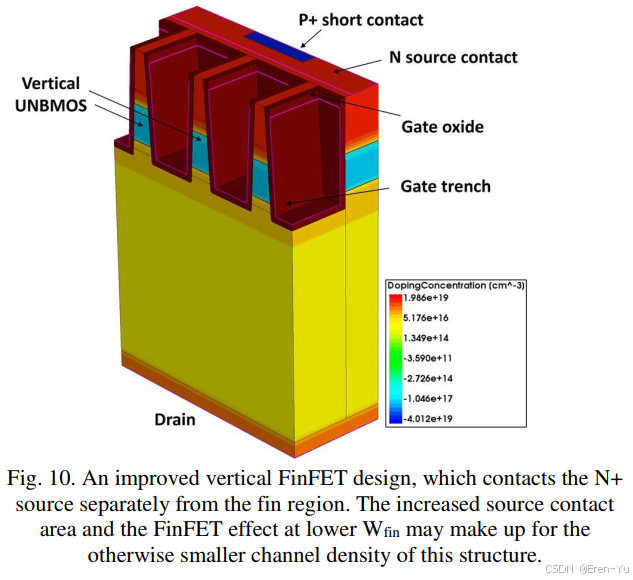

- 接触电阻优化:针对源极接触电阻( R source R_{\text{source}} Rsource)随鳍密度增加的问题,提出三维分离式接触设计(图10),将n+源极与p+体接触分离至鳍区域外,扩大接触面积以降低电阻。

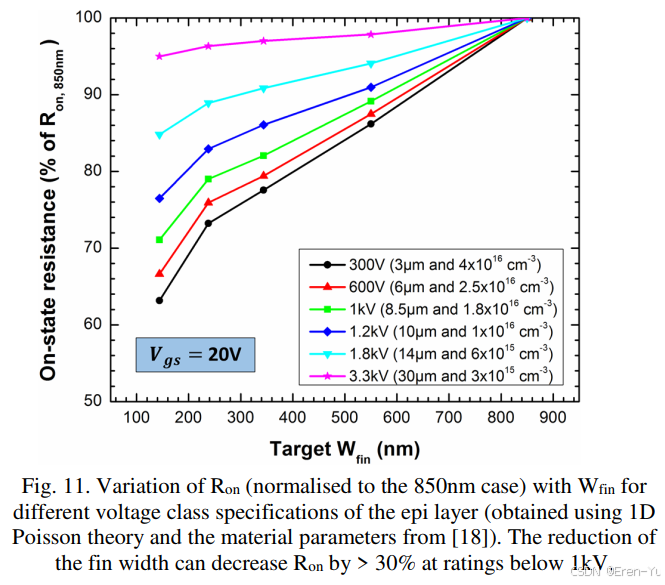

- 电压等级适应性分析:基于1D泊松方程和材料参数(文献[18]),预测不同电压等级下FinFET对导通电阻的改善效果(图11),指出其在<1kV应用中的优势。

5. 综合方法特点

- 实验与仿真的闭环验证:通过实验数据校准TCAD模型,利用模型反哺物理机制分析,形成“设计-制造-测试-优化”的迭代流程。

- 多物理场耦合:综合电学、热学(隐含)、材料界面特性,全面评估器件性能限制因素。

- 跨尺度设计:从纳米级鳍结构(144nm)到宏观器件布局(活性区域≈0.6mm²),实现微纳工艺与系统级优化的协同。

总结:文章采用“实验制备→TCAD建模→数据验证→理论分析→设计优化”的多层次研究方法,通过工艺创新与物理模型深度结合,系统揭示了垂直SiC FinFET的性能潜力与挑战,为下一代功率器件的开发提供了方法论范例。

文章的创新点

1. 首次实现垂直常关型高压SiC FinFET

- 技术突破:

首次成功制备了垂直结构的常关型(Normally-off)SiC FinFET,并实现以下核心性能指标:- 击穿电压达1kV,适用于高压功率应用;

- 超低导通电阻( R on = 0.7 m Ω ⋅ cm 2 R_{\text{on}} = 0.7 \, \text{m}\Omega \cdot \text{cm}^2 Ron=0.7mΩ⋅cm2),显著优于传统SiC MOSFET;

- 阈值电压( V th = 2.2 V V_{\text{th}} = 2.2 \, \text{V} Vth=2.2V)稳定可靠,满足工业级需求。

- 结构创新:

基于144nm鳍宽沟槽技术(图1),通过优化栅极氧化层(沿(1-100)晶面生长,锥角3.5°)和p-well掺杂,解决了SiC器件中界面态密度高、迁移率低的关键难题。

2. 揭示SiC FinFET效应及其三重作用机制

- 理论创新:

首次在SiC器件中系统阐释了FinFET效应的物理机制,提出其通过以下三重作用提升性能:- 减少耗尽电荷,增强反型层电荷密度(在相同 V gs V_{\text{gs}} Vgs下);

- 减弱表面散射,使沟道远离SiC/SiO₂界面;

- 降低横向电场,进一步提升载流子迁移率。

- 实验验证:

通过TCAD模拟与实验数据对比(图5-6),证明144nm鳍宽器件中体传导占比显著增加,阈值电压降低,跨导特性更优,验证了FinFET效应在SiC中的有效性。

3. 开发高精度TCAD模型并实现工艺-性能闭环优化

- 方法创新:

基于Synopsys Sentaurus构建了三维校准TCAD模型(图4),通过以下策略提升仿真精度:- 引入库仑散射、表面声子散射和粗糙度散射的综合迁移率模型;

- 结合实验数据动态校准界面态密度( D it D_{\text{it}} Dit)和固定电荷密度( N fs N_{\text{fs}} Nfs)。

- 应用价值:

该模型不仅成功预测了不同鳍宽器件的阈值电压偏移趋势(图5b-f),还为后续设计优化(如三维分离式接触布局,图10)提供了理论依据,形成“工艺参数→电学特性→结构改进”的闭环优化路径。

4. 提出针对SiC FinFET的改进设计与应用策略

- 设计创新:

- 三维分离式接触设计(图10):通过将n+源极与p+体接触分离至鳍区域外,扩大源极接触面积,显著降低接触电阻( R source R_{\text{source}} Rsource),解决了鳍密度增加导致的性能瓶颈。

- 多电压等级适应性分析:基于1D泊松方程(图11),量化了FinFET效应在不同电压等级下的增益,指出其在<1kV应用中可实现导通电阻 R on R_{\text{on}} Ron降低30%以上,为SiC与GaN器件的竞争提供技术路线。

- 工艺创新:

提出通过超窄鳍刻蚀技术(目标鳍宽30-150nm)结合先进钝化工艺,进一步挖掘SiC FinFET潜力,为未来器件微缩指明方向。

5. 挑战中挖掘新机遇:定义SiC FinFET的应用边界

- 系统性创新:

明确SiC FinFET的适用场景与限制:- 优势领域:1kV以下电压等级,通过FinFET效应实现低导通电阻,直接挑战GaN器件;

- 高压限制:在>1kV应用中,因漂移电阻主导,FinFET的增益被削弱,需结合其他技术(如超结结构)提升性能。

- 前瞻性结论:

提出SiC FinFET需通过电热耦合设计和多物理场协同优化,解决高功率密度下的可靠性问题,为其在新能源、智能电网等领域的应用铺平道路。

总结:本文通过结构创新(垂直FinFET)、理论突破(FinFET效应机制)、方法革新(高精度TCAD模型)与设计策略优化(三维分离式接触),系统性提升了SiC功率器件的性能边界,并为其在高压、高功率场景中的实际应用提供了全新解决方案。

文章的结论

1. 垂直SiC FinFET的核心性能验证

- 首次成功实现了击穿电压1kV、导通电阻0.7mΩcm²、阈值电压2.2V的垂直常关型SiC FinFET,验证了其作为高压功率器件的可行性。

- 144nm鳍宽设计通过FinFET效应显著提升迁移率,在低电压等级(<1kV)下,导通电阻( R on R_{\text{on}} Ron)较传统结构降低超30%(图11),展现出与GaN器件竞争的技术潜力。

2. FinFET效应的作用机制与边界条件

- FinFET效应通过减少耗尽电荷、减弱表面散射、降低横向电场三重机制提升性能,但其效果高度依赖鳍宽度(需控制在30-150nm)。

- 适用场景:

- 优势领域:1kV以下应用场景,FinFET效应可显著降低 R on R_{\text{on}} Ron,助力SiC器件替代GaN;

- 高压限制:>1kV时,漂移电阻主导,FinFET增益有限,需结合超结(Super Junction)等技术突破性能瓶颈。

3. 关键挑战与改进方向

- 工艺挑战:

- 超窄鳍结构(<150nm)对SiC刻蚀、钝化及界面控制提出极高要求,需开发更高精度的纳米制造技术。

- 设计挑战:

- 鳍密度增加导致源极接触电阻( R source R_{\text{source}} Rsource)上升,需通过三维分离式接触布局(图10)优化载流子路径,平衡通道密度与接触面积。

- 可靠性挑战:

- 高功率密度下电热耦合效应可能限制器件寿命,需结合多物理场仿真优化散热与电学性能。

4. 未来前景与应用潜力

- 低电压领域:通过优化鳍密度(如进一步缩小至30nm)与接触设计,SiC FinFET有望在新能源汽车、数据中心电源等场景中实现高效、紧凑的功率转换。

- 工艺创新:开发新型钝化层(如高k介质)和界面工程,降低界面态密度( D it D_{\text{it}} Dit),进一步提升迁移率。

- 系统集成:探索SiC FinFET与封装技术(如双面冷却)、驱动电路的协同设计,推动其在智能电网、可再生能源系统中的规模化应用。

总结:本文通过实验与仿真结合,证实了垂直SiC FinFET在高压、高效功率器件中的突破性潜力,明确了其性能优势与适用边界,并为解决工艺与设计挑战提供了创新方案。未来,随着纳米制造技术与多物理场优化方法的进步,SiC FinFET有望成为下一代功率电子系统的核心器件。

1043

1043

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?