借鉴了:https://blog.csdn.net/xiaoqingcaigege/article/details/84454679

以xilinx 7系列FPGA为例:

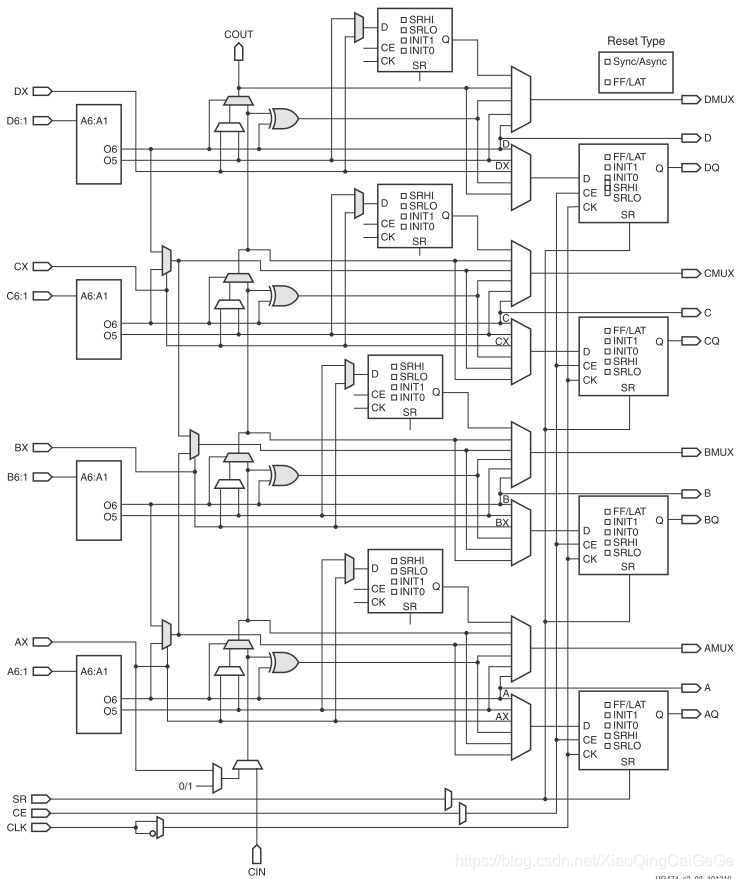

Xilinx的官方文档在介绍FPGA的逻辑资源时通常是按照CLB(Configurable Logic Block)来介绍,把CLB作为FPGA里的最小逻辑单元。但是CLB是由2个slice构成,因此平时大家都把slice挂嘴边,称为最小的逻辑单元,很少提起CLB。因此本篇咱们就简要聊一聊slice的功能。对于大部分应用,咱们不必深入了解slice,写好代码后FPGA的开发软件会自动帮助咱们布局布线,所以本篇以了解为主,当然如果您是高级用户,是大佬级FPGA专家,就另当别论。

7系列FPGA的slice包含4个部分:

(1)

逻辑功能产生器,也就是咱们常说的查找表LUT,1个slice里包含4个6输入的查找表。

*4

*4

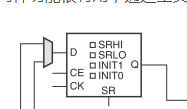

(2)

存储单元,也就是常说的触发器,1个slice里包含8个触发器。每4个触发器为一组,可配置成D触发器或锁存器。

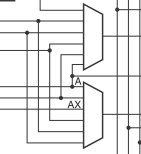

(3)

多路复用器,也就是1位宽的数据选择器mux,数量非常多,足够使用。

(4)

进位逻辑(carry chain),另外这不是或门,而是异或门。这是FPGA中自带的进位链(Carry Chain)逻辑。一般当你实现诸如计数器这种可能有进位逻辑的设计可能会调用到这部分资源

因此,许许多多的slice相结合,再加上全局时钟就能实现复杂的数字功能!另外,咱们还得提到重要的一点,FPGA里的slice有2种,一种被称为sliceL,另一种被称为sliceM,有的CLB由2个sliceL构成,有的则是由1个sliceL和一个sliceM构成。SliceM除了基本功能外,可以实现RAM和移位寄存器的功能,这两种功能很有用,通过工具软件可以自动实现,不用咱们操心,咱们只需要知道这点就够了。贴上一张sliceL的结构图。

1820

1820

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?