4 DDR5 SDRAM命令描述和操作-30

4.30 决策反馈均衡(DFE)

4.30.1 简介

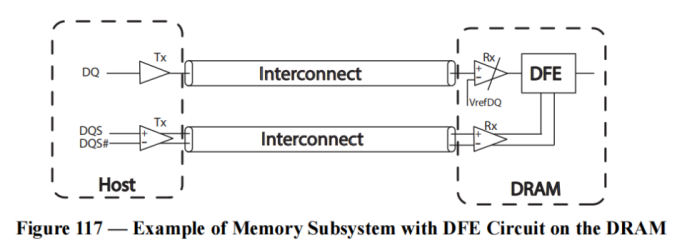

在数据速率大于等于3200MT/s时,由于符号间干扰(ISI)而引起的信号衰减预计会增加,并且DRAM引脚处的数据眼预计会闭合。由于内存子系统中存在许多阻抗不匹配点,导致内存通道非常反射,因此预计反射引起的ISI会增加。传统的使用输入眼掩码来表征接收器的方法已经不再足够。DDR5需要使用均衡来帮助在数据被接收器锁存后改善(或打开)数据眼。选择了4个延迟的决策反馈均衡(DFE)来帮助均衡DQ信号,而不会放大由插入损耗和反射引起的噪声,这是其他均衡技术(例如CTLE)的常见副作用。图117显示了具有DRAM上包含DFE电路的内存子系统的示例。

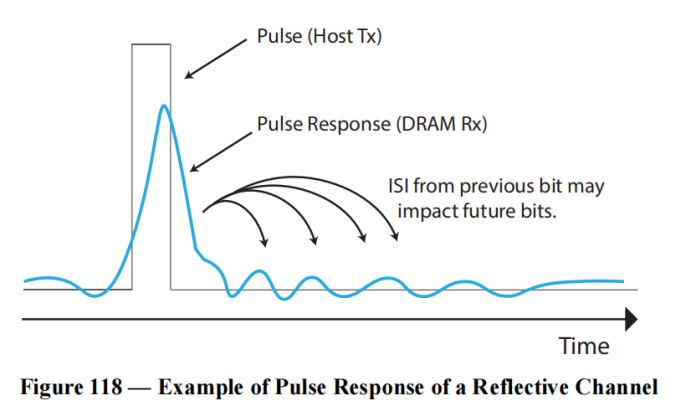

4.30.2 反射存储通道的脉冲响应

在内存子系统中,像反射主导的通道预计会由于插入损耗和反射效应而导致DRAM引脚处的数据眼大幅减小。图118展示了一个非常反射通道的脉冲响应可能的样子。信号的衰减和振荡会导致DRAM引脚处的数据眼闭合。此外,振荡还会影响发送到通道中的未来位,也就是说,如果脉冲响应是针对位n的情况,那么来自位n的振荡会影响未来位n+1、n+2、n+3、n+4等的信号完整性。换句话说,任何位(例如位n)的信号完整性都可能受到前面位n-1、n-2、n-3、n-4等信号的影响。

4.30.3 DFE的组成

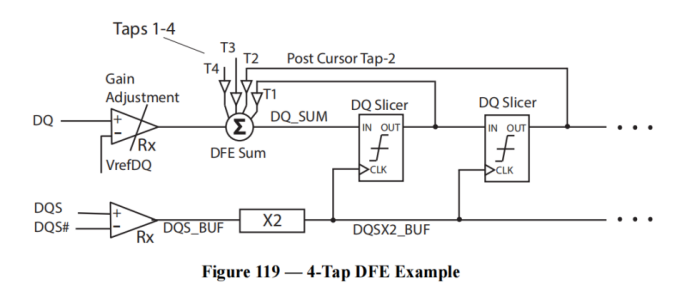

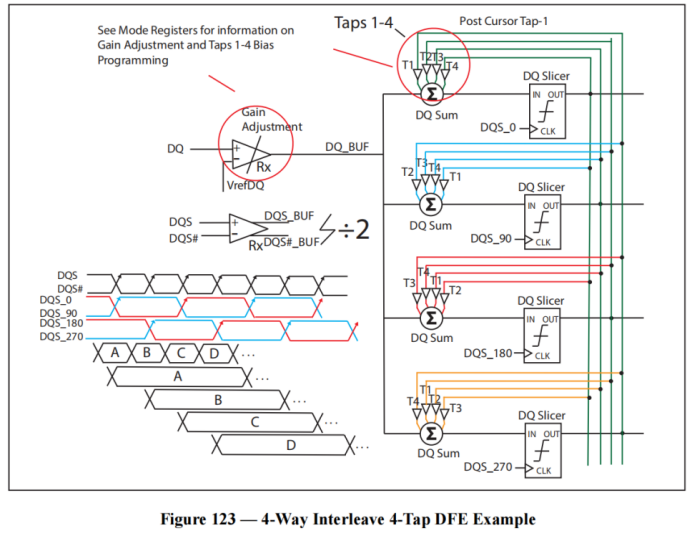

4-tap DFE子系统包括增益放大器、DFE累加器、4个DQ切片器(也称为Tap),其输出回路返回到DFE累加器,以及每个Tap的系数乘法器(图119)。前端的增益控制用于确保游标或当前位与通道所需的ISI修正之间处于一致关系。T1、T2、T3、T4这几个Tap的系数提供了通过添加或减去前面位的ISI效应来对当前位的修正。

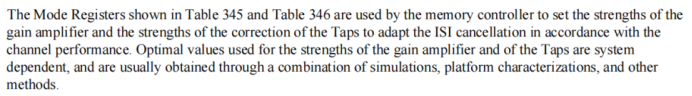

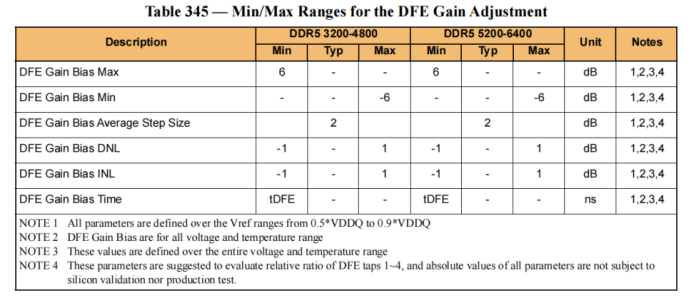

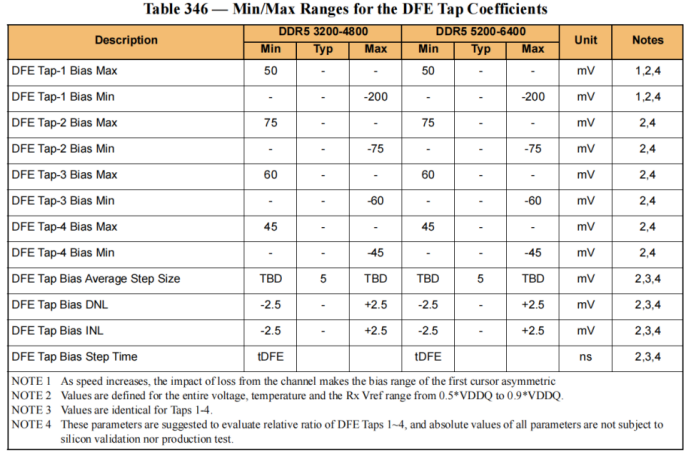

表345和表346中显示的模式寄存器由内存控制器用于设置增益放大器的强度和Tap的纠正强度,以根据通道性能来适应ISI消除。用于增益放大器和Tap强度的最佳值是与系统相关的,通常通过模拟、平台特性分析和其他方法得出。

注1:所有参数均在Vref范围从0.5*VDDQ到0.9*VDDQ内定义。

注2:DFE增益偏置适用于所有电压和温度范围。

注3:这些值在整个电压和温度范围内定义。

注4:这些参数建议用于评估DFE Tap 1~4的相对比例,所有参数的绝对值不需要经过硅验证或生产测试。

注1:随着速度的增加,通道损耗对第一个游标的偏置范围产生不对称的影响。

注2:这些值适用于整个电压、温度和Rx Vref范围从0.5*VDDQ到0.9*VDDQ。

注3:Taps 1-4的值相同。

注4:这些参数建议用于评估DFE Tap 1~4的相对比例,所有参数的绝对值不需要经过硅验证或生产测试。

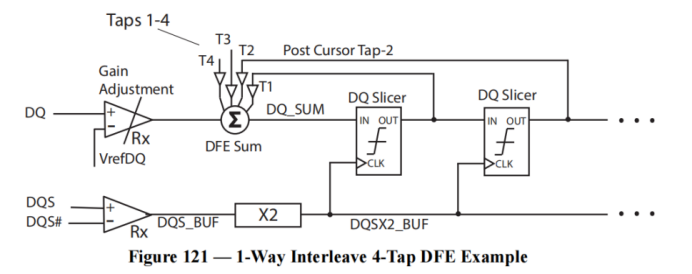

DRAM可以实现1路交织、2路交织或4路交织的4-tap DFE存储电路。1路交织的4-tap DFE架构(图121)需要一个与奈奎斯特速率相匹配的时钟倍频器,并且DQ切片器的输出速度与接收到的数据相同。

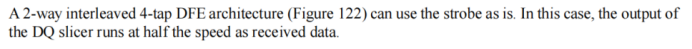

2路交织的4-tap DFE架构(图122)可以直接使用时钟信号。在这种情况下,DQ切片器的输出速度是接收到的数据速度的一半。

4路交织的4-tap DFE架构(图123)需要一个分频时钟。在这种情况下,DQ切片器的输出速度是接收到的数据速度的1/4。

1376

1376

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?