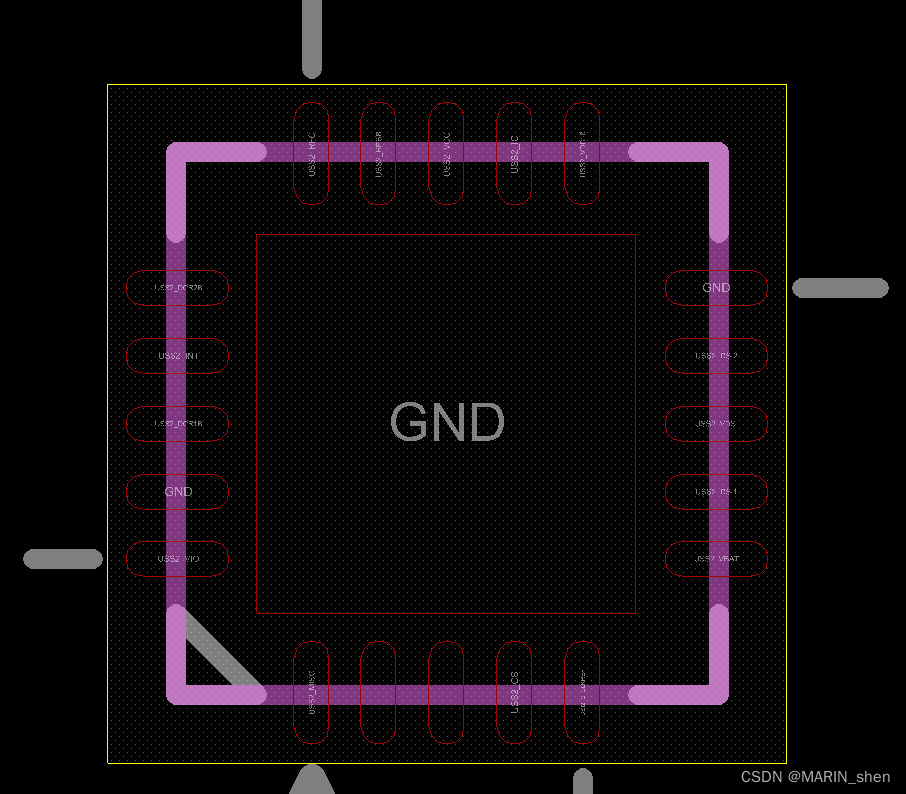

提起place bound这个名词想必不论是做过PCB设计的还是封装设计应该都不陌生吧?尤其是做封装设计的,是元器件封装实际大小,用来防止两个元器件叠加在一起不报错,外框尺寸需要包括焊盘在内。这个尺寸或者区域就表示了这个器件焊接到板子上以后,器件的外形尺寸加焊盘占用的总的空间,如下图所示:

最外层的是器件的place bound层,粉色的线是代表这器件的装配层丝印(器件的本体尺寸大小),白色的是器件的丝印层(用来标记元器件的安装位置,方向,大致的占位位置)。

一般来说一尺寸上 assembly<= silkscreen <=place bound。(这个silkscreen是建封装的package丝印不是我们后期调丝印的添加的board Geometry silkscreen )然而对于我们做PCB设计者来说,器件的place bound一般都是布局的时候打开,对于放置器件有干涉的,这个在ALLEGRO软件中是可以通过设计DRC来识别你的布局是否有干涉:

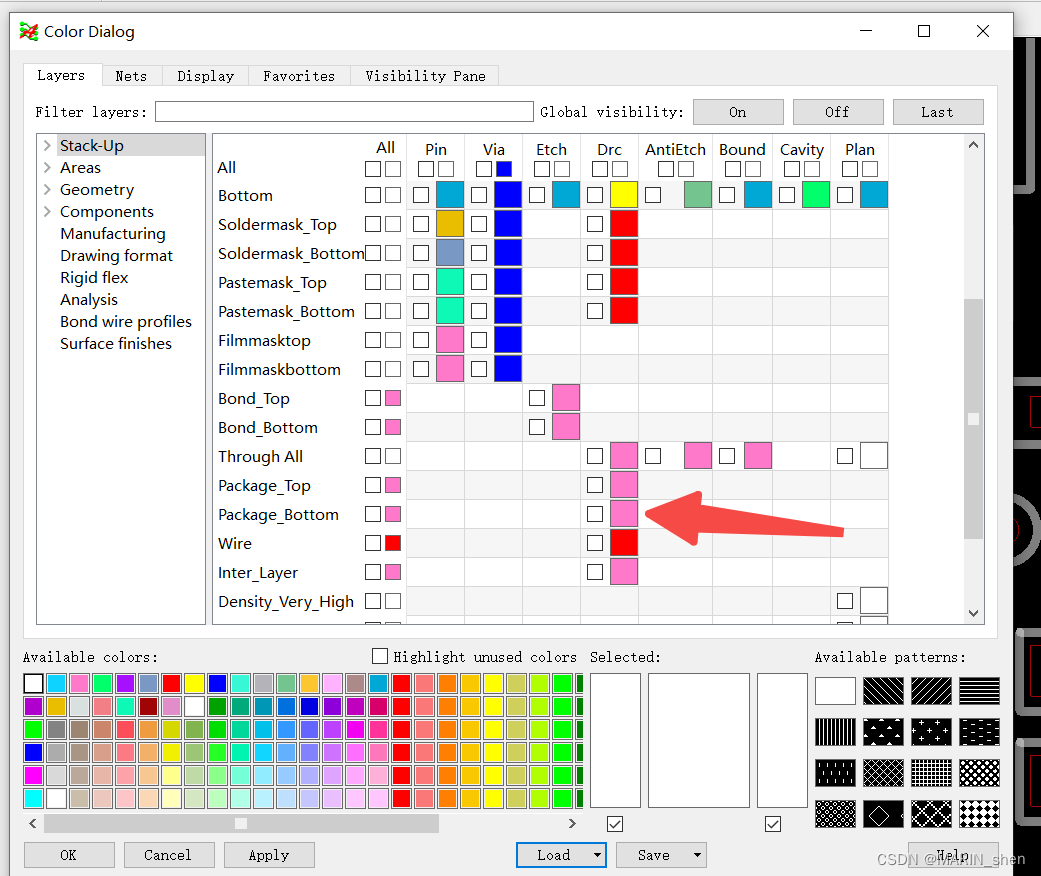

步骤如下所示:

首先打开Display--color ,然后在Stack-Up目录下,在右侧栏目将 Package_top / Package_Bottom勾选上,然后保存设置。布局的时候如果器件放置时发生Place_bound干涉,就会弹出DRC报错。

这个设置对于我们pcb设计者很方便友好的,但是有时候会出现以一个问题就是我们给结构工程师导出的STP文件时候,结构那边看到的器件模型是我们建的place bound尺寸大小而不是器件真正的本体尺寸,除非你建的封装库的时候是以器件的assembly尺寸去画place bound尺寸大,这样结构工程师那边导入他们的软件中器件的模型才是符合规格书的尺寸,也就是器件本体的尺寸的。这个时候就比较麻烦了,因为你建的封装库的标准不可能有两个,要么就是按照器件的本体尺寸来建器件封装的place bound;要么就按照正常的尺寸来建器件封装的place bound(正常的标准:assembly<= silkscreen <=place bound)

上图就是器件的place bound建的比较小,比焊盘还内缩了一些距离,这样的话对于结构那边是比较友好的,器件的本体尺寸是和place bound尺寸一样的,也符合手册的尺寸要求的。但是这个对于我们做PCB布局的时候就不太友好了,这样的话你就不能通过软件设置器件place bound的DRC来去判别器件是否有干涉了。

古人有云鱼与熊掌不可兼得,想要两个都要不太容易的。我这边处理的方式就是提前和结构工程师那边沟通好哪些芯片需要做结构上的特殊设计,我们就把这些芯片的place bound建的和器件的本体一样(器件的place bound尺寸建的和器件的assembly的尺寸一样)。其他的器件的place bound就按照常规的设计经验做即可(assembly<= silkscreen <=place bound),这样结构那边可能在做芯片散热凸台或者是结构上的特殊设计的时候就可以根据我们PCB工程师导出的STP文件更加准确的识别器件的模型了,这样他们结构那边就不需要做太大的散热凸台的尺寸,这样留给我们布局的空间也就多了一些了。

最后记得建器件的place bound的时候加上器件的高度信息,至于如何添加器件的高度信息我在这边再啰嗦一下吧,可能有的不会建封装的朋友对于这个操作可能不是很熟悉,具体操作如下所示

1,首先打开set up—Areas—Package Height

然后单击选中你建的place bound,在右边的options就会出现place bound设置选项,按照规格书填上具体的封装高度,需要注意的是这个高度一般是按照手册上推荐的值加上+的误差值。

还有就是这个高度信息数值也是不能随便填写的,不然你导出给结构那边的STP文件他们打开就是高低不平的模型了。

小编有一个硬件同事最近也刚刚好问我如何在allegro软件中查看器件的高度信息,具体的方法有两个:其一就是刚刚上面提到的如何建器件高度器件的设置也是查看器件高度信息的设置;另外一个就是在allegro软件中通过show器件的PLACE_BOUND的shape属性来查看器件的高度信息。

以上就是小编在做PCB设计的时候对于器件的PLACE_BOUND尺寸设计的一些经验总结,希望能够帮助到大家。当然我说的也仅仅是个人观点,有不同之处还望路过的朋友们指点一二。

283

283

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?