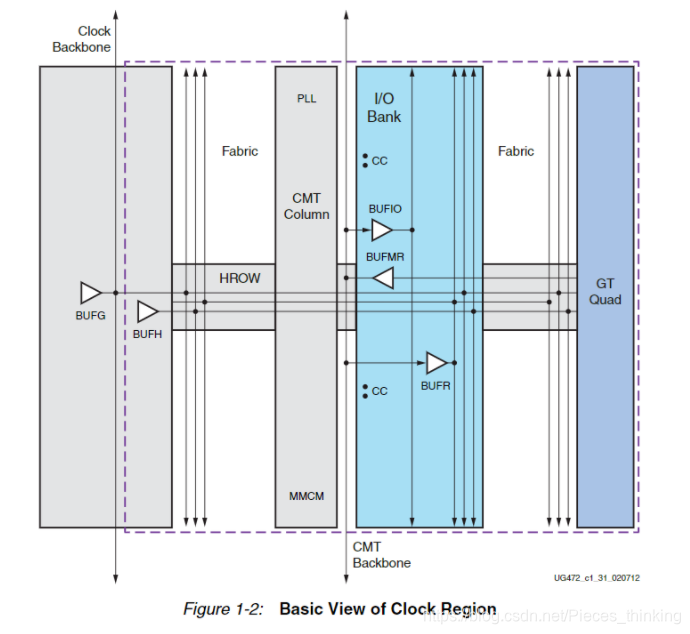

Xilinx的7系列时钟输入有SRCC和MRCC。在手册上有描述,SRCC可用于本时钟区域,MRCC用于本时钟区域和相邻时钟区域。单看这个就有些困惑了,那难不成还连接不到全局时钟了。官方手册中有下面这个图,可以看出SRCC和MRCC都是可以连接到全局时钟的。这个图由于有点具体,不太好理解。

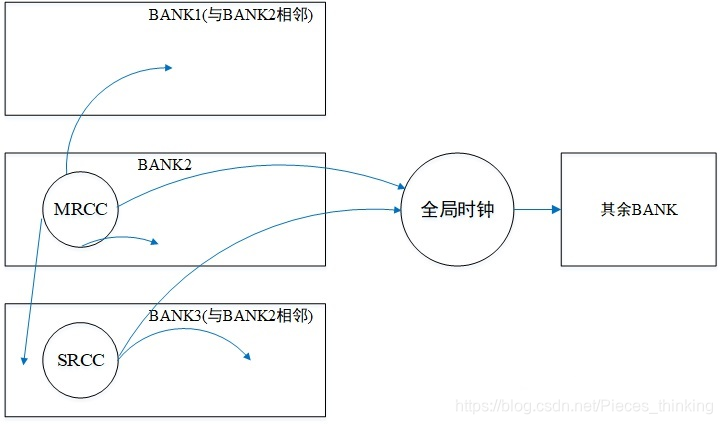

看下面这个图,首先MRCC和SRCC都是可以连接到全局时钟的,但是全局时钟的资源有限。如果程序较大都使用全局时钟的话,那时钟资源就不够用了。SRCC可用于本区域时钟这个比较好了解,MRCC用于相邻的区域该这么理解,MRCC通过不同于全局时钟的渠道可以到达相邻的区域。虽然通过手册可以看到芯片的各个区域分布,但是这个还是最好交给EDA自己优化。如下图BANK1和BANK3可以使用BANK2的MRCC分上来的时钟,没必要先将BANK2的MRCC连接到全局时钟再连接到BANK1和BANK3,这样不但节省了全局时钟资源,而且路径更短。

本文探讨Xilinx 7系列FPGA中的SRCC和MRCC时钟输入资源。详细解释这两种资源如何用于本区域及相邻区域,并讨论如何合理分配全局时钟资源以优化设计。

本文探讨Xilinx 7系列FPGA中的SRCC和MRCC时钟输入资源。详细解释这两种资源如何用于本区域及相邻区域,并讨论如何合理分配全局时钟资源以优化设计。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?