Q:接下来我们会分四篇介绍分频器并在DE2-115开发板上设计实现。第一篇介绍以D触发器方式实现偶数分频器的概念原理。

A:分频即将一个时钟信号通过一定的电路结构转变成不同频率的时钟信号。按分频方式可分为偶数分频、奇数分频和半整数分频。对于2的幂次级的偶数分频,可以用简单的D触发器通过时钟的上升沿或下降沿到来时进行翻转得到,这样信号的两个状态所占时间长度相同,所以它的输出时钟的占空比为50%,且是不可变的。

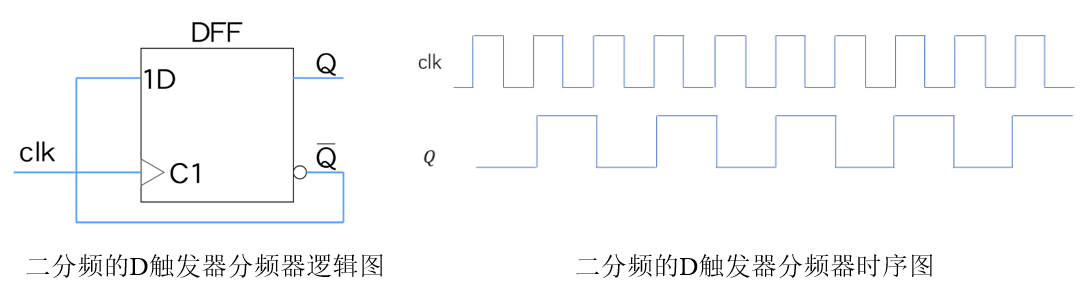

之前我们设计实现了基本D触发器,以D触发器方式实现偶数分频器,就是将D触发器的\overline Q端接到D端,可以实现二分频,即在每个时钟周期,D触发器的Q输出翻转一次。

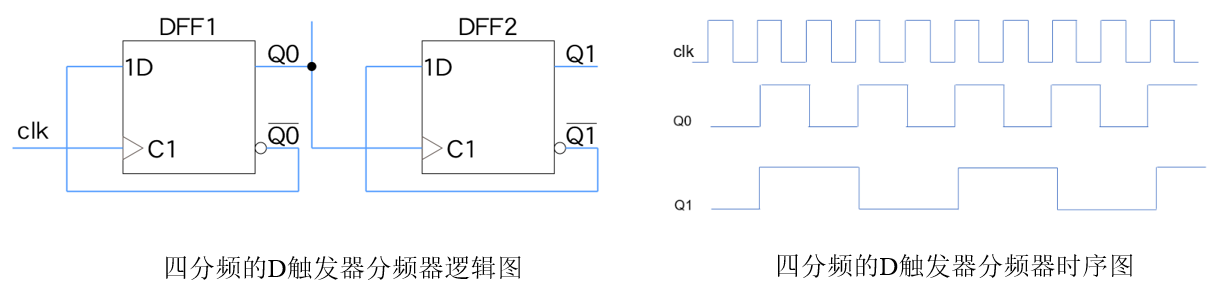

将两个D触发器级联可以实现4分频,以此类推,当级联的D触发器为N个时,分频结果为2的N次方分频。

本文将介绍如何利用D触发器构建偶数分频器,包括二分频和多级联D触发器实现更高分频。重点讲解了在DE2-115开发板上的应用,以及输出时钟的特性。

本文将介绍如何利用D触发器构建偶数分频器,包括二分频和多级联D触发器实现更高分频。重点讲解了在DE2-115开发板上的应用,以及输出时钟的特性。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?