synopsys PCIE IP协议解析

1.Overview

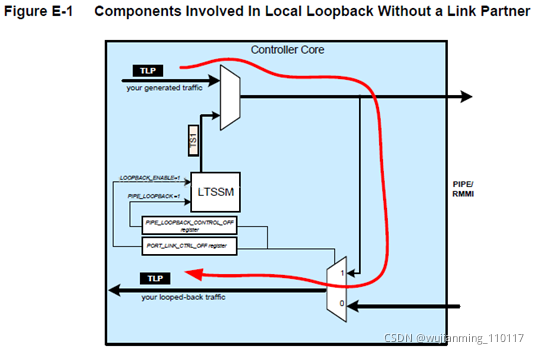

Core支持单个Pcie内核的Loopback功能,该功能主要为了做芯片验证,以及在没有远程接收器件的情况下完成自己的回环。同时,Core也支持有远程接收器件的loopback,在该中情况下,远程接收器件称为loopback slave。该种模式可以用来完成板级的debug,BER测试,系统调试。

在做Loopback的时候需要注意将“Link up”强制写成1(根据specification该位应该是0),造成系统处于L0状态的假象,以便系统完成link的initialize。

1.1 Local Digital Loopback (PIPE/RMMI)

本地的Loopback分为3个阶段:Entering Local Loopback、In PIPE Loopback、Exiting Local Loopback

1.1.1 Entering Local Loopback

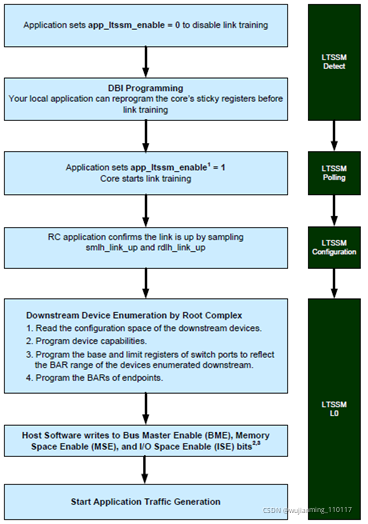

Loopback将PIPE/RMMI RX 与自身的PIPE/RMMI TX相连,在该种Loopback模式下,只能运行LTSSM(link training and statues statemachine),在该状态下无法进行自身的training和进入到L0状态。进入local loopback的流程如下:

Ø 先要disable“Gen3 Control Register GEN3_RELATED_OFF.

Ø Set the PIPE_LOOPBACK bit in the PIPE_LOOPBACK_CONTROL_OFFregister.

Ø Set the LOOPBACK_ENABLE bit in the PORT_LINK_CTRL_OFF register.

1.1.2 In PIPE Loopback

在该Loopback 模式下,通过虚拟系统进入L0状态,可以进行link initialize。在进入了Loopback mode以后,Core会为VC0的flow control进行初始化。当该初始化完成后,application就可以通过XALI0/1/2接口发送TLP。当TLP包 loopback回来后,application 需要发送complete以响应自身发的TLP包。当TLP和DLLP被发出同时被收回时,接口将对自身启动flow control。在L0阶段,当TLP因为link 错误而没有被接收到时,TLP包将会被重新发送。TLP的发送将会像正常的link一样进行credit 检测接收,也会在L0阶段进行正常的error check和filter check。

MessageConsiderations

当接口是一个上行接口(USP),必须保证没有使能生成的error message。当有错误发生在PCIelink时,同时使能了error message的生成,那么USP将会生成一个 Error Message。有接口生成的数据包将会loopback到自身USP不期望接收message,将会生成一个附加的message。

在进入L0阶段时,DSP接口必须自动的发送Set_Slot_Power_Limitmessage该message将会被自身发送并且接收回来。但是DSP接口是不期望接收到Set_Slot_Power_Limit message的,所有该message将会被作为无效的message,同时Device Status 中的unsupported requestdetected bit将会被置位。

在DSP接口中,Core内部生成的message 将会与application通过XALI0/1/2生成的TLP混合在一起发送。

Enumeration and BAR Setup

必须配置BARS(USP),memory/IO rangs(DSP),将me

本文详细介绍了Synopsys PCIE IP协议的Local Digital Loopback功能,包括Entering Local Loopback、In PIPE Loopback和Exiting Local Loopback三个阶段。在Loopback模式下,文章强调了设置流程、Gen3操作、配置流程以及各模块间的交互。同时,讨论了在不同阶段如何配置和操作,以确保正确执行Link Training和系统调试。

本文详细介绍了Synopsys PCIE IP协议的Local Digital Loopback功能,包括Entering Local Loopback、In PIPE Loopback和Exiting Local Loopback三个阶段。在Loopback模式下,文章强调了设置流程、Gen3操作、配置流程以及各模块间的交互。同时,讨论了在不同阶段如何配置和操作,以确保正确执行Link Training和系统调试。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

297

297

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?