台积电5nm光刻技术

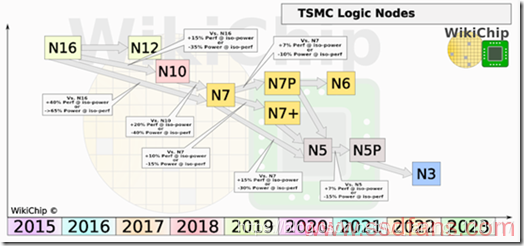

在IEEE IEDM会议上,台积电发表了一篇论文,概述了其5nm工艺的初步成果。对于目前使用N7或N7P工艺的客户来说,下一步将会采用此工艺,因为这两种工艺共享了一些设计规则。新的5nm制程使用了台积电的第五代FinFET技术,在7纳米基础上提供一个完整的工艺节点,并使用EUV极紫外光刻技术扩展到10多个光刻层,与7纳米相比减少了生产总步骤。

关键数字

如果只是来了解关键数字的,那答案就在这里。台积电表示,5nm EUV工艺使得晶体管密度增加到大致1.84倍,能效提升15%,功耗减少30%。目前的测试芯片(包括256 Mb的SRAM和一些逻辑单元),平均良率80%,峰值良率达到90%以上,不过这些芯片相对简单,如果放到复杂的移动芯片上,良率要低得多。该技术2020年上半年量产,基于5nm的芯片在2020年下半年面世。

台积电的7nm工艺在使用高密度库时,每平方毫米可生产近1亿个晶体管,约为9627万个,这意味着5nm应该是每平方毫米1.7714 亿个晶体管左右。

详解良率

作为风险试产的一部分,代工厂会生产大量的测试芯片,以验证其新工艺可以达到预期。对于5nm制程,台积电披露了两种测试芯片:一种基于SRAM,另一种结合了SRAM、逻辑单元和IO单元。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

822

822

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?